#### SECURING ACCESS IN EMBEDDED SYSTEMS VIA DMA PROTECTION AND LIGHT-WEIGHT CRYPTOGRAPHY

by

#### FILIPPOS – GEORGE KOLYMPIANAKIS

#### THESIS

submitted in partial fulfillment of the requirements for the

#### degree MASTER OF SCIENCE

Hellenic Mediterranean University

Department of Electrical and Computer Engineering

Approved by

Supervisor: Dr Kornaros George

#### Abstract

Embedded systems are the driving force for technological development in many domains such as automotive, healthcare and industrial control. Security is an important aspect of embedded system design. As more and more computational and networked devices are integrated into all aspects of our lives security becomes critical for the dependability of all smart or intelligent systems built upon these embedded systems. Security is provided through a DMA controller which is operated under certain constraints and with the use of light-weight cryptography as an extended mechanism to safeguard the confidentiality and integrity of stored and transmitted information.

Direct memory access (DMA) protection is a necessity, especially in case of RAM memories where the most of accessible data are located. Different devices or users have different rights to data contained in each memory, which is the main reason to use a firewall as a method to protect the data being accessed. Penetrating a device from high speed ports that permit DMA is an important issue in embedded systems. A DMA firewall prevents physical connections from DMA attacks so that each device has restricted access for DMA transfers using memory limitations and device ID. In that way attackers are prevented from stealing data or cryptographic keys, install or run spyware and other exploits or modify the system to allow backdoors or other malware

# Table of Contents

## Contents

| Abstract                                    | 2 |

|---------------------------------------------|---|

| Table of Contents                           | 3 |

| List of Figures                             | 5 |

| Acknowledgements                            | 7 |

| 1. Introduction                             | 3 |

| 1.1 General                                 | 3 |

| 1.2 Motivation                              | ) |

| 1.3 Contribution                            | L |

| 1.4 Organization                            | L |

| 2. Basic Principles 12                      | 2 |

| 2.1 Embedded Systems                        | 2 |

| 2.2 Direct Memory Access                    | 3 |

| 2.3 Cryptography14                          | 1 |

| 2.3.1 Advanced Encryption Standard14        | 1 |

| 2.3.2 True Random Number Generator          | 7 |

| 2.4 Xilinx Vivado1                          | 7 |

| 2.4.1 Vivado High Level Synthesis           | 7 |

| 2.4.2 Vivado                                | 3 |

| 2.4.3 Software Development Kit 19           | ) |

| 2.5 ZedBoard                                | ) |

| 3. Embedded Systems Security 22             | 2 |

| 3.1 Constrains, Vulnerabilities and Attacks | 3 |

| 4. Background on Related Work 27            | 7 |

| 5. Design and Architecture                  | 1 |

| 5.1 DMA Controller                          | 1 |

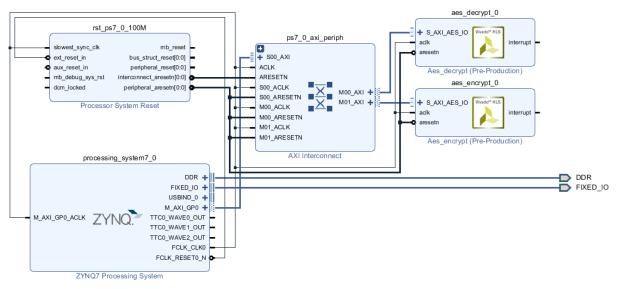

| 5.2 AES IP-Blocks                           | 7 |

| 5.2.1 AES Encryption Module                 | 3 |

| 5.2.2 AES Decryption Module                 | L |

| 5.3 Cryptographic Co-Processor              | 3 |

| 5.4 True Random Number Generator            | 1 |

| 5.5 Secure Embedded System                  | 5 |

| 5.5.1 Schematic Design                      | 5 |

| 5.5.2 Architectural Implementation          | 7 |

| 6. Evaluation and Performance  | 51 |

|--------------------------------|----|

| 6.1 Module Evaluation          | 51 |

| 6.2 System Analysis            | 59 |

| 6.3 System Comparison          | 64 |

| 6.4 Applications6              | 64 |

| 7. Conclusion and Future work6 | 66 |

| References6                    | 68 |

# List of Figures

| Figure 1: Typical DMA                                                                | . 13 |

|--------------------------------------------------------------------------------------|------|

| Figure 2: Steps of AES Encryption (Wikipedia)                                        | . 15 |

| Figure 3: AES algorithm                                                              |      |

| Figure 4: ECB vs CBC (Wikipedia)                                                     | . 16 |

| Figure 5: Vivado HLS                                                                 | . 18 |

| Figure 6: Vivado Design Software                                                     | . 19 |

| Figure 7: Software Devepopment Kit                                                   | . 20 |

| Figure 8: Zedboard                                                                   | . 21 |

| Figure 9: Project Schematic                                                          | . 35 |

| Figure 10: Main arguments (ARM9)                                                     | . 36 |

| Figure 11: Boundaries Channel (Microblaze)                                           | . 36 |

| Figure 12: Ports of DMA                                                              | . 36 |

| Figure 13: Calculating the Limits Source and Destination                             | . 36 |

| Figure 14: SubBytes in C-code                                                        | . 38 |

| Figure 15: ShiftRows in C-code                                                       | . 38 |

| Figure 16: MixColums in C-code                                                       | . 39 |

| Figure 17: AddRoundKey in C-code                                                     | . 39 |

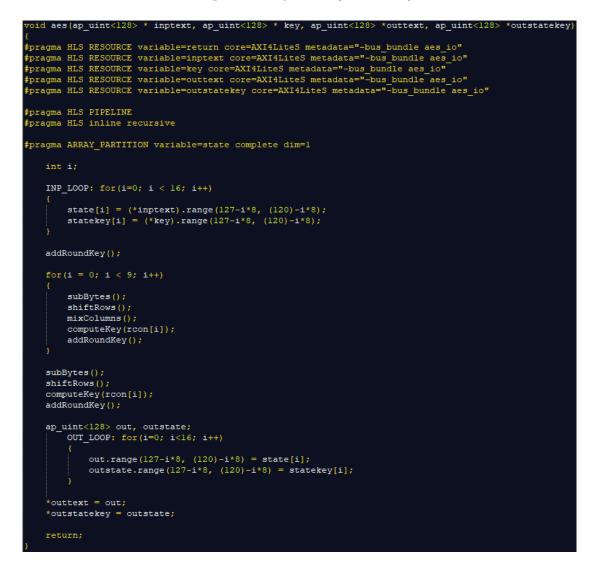

| Figure 18: Main function to produce the ciphertext                                   | . 40 |

| Figure 19: Changes made in order to synthesize a Hardware IP Block                   | . 40 |

| Figure 20: AddRoundKey in C-code                                                     | . 41 |

| Figure 21: ShiftRowsInv in C-code                                                    | . 42 |

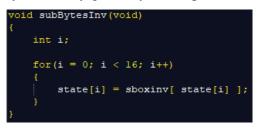

| Figure 22: SubBytesInv in C-code                                                     | . 42 |

| Figure 23: MixColumsInv in C-code                                                    | . 42 |

| Figure 24: Main function to produce plaintext synthesizable for a Hardware IP Block  | . 43 |

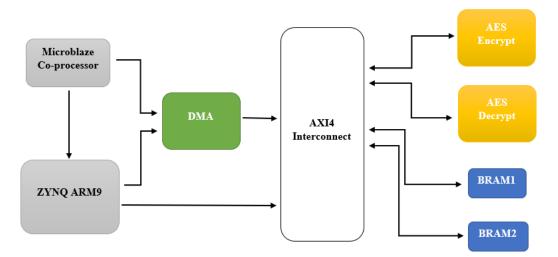

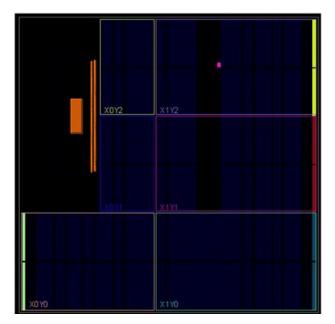

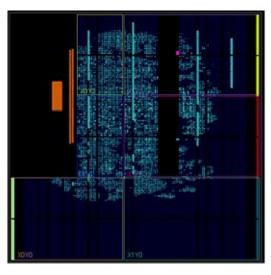

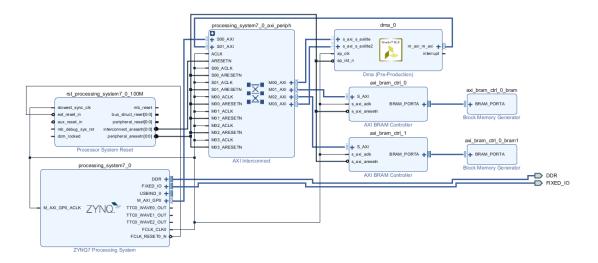

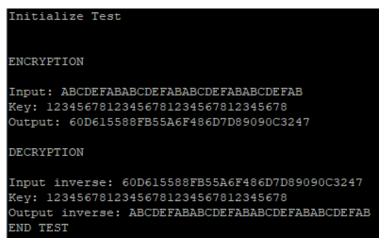

| Figure 25: A secure Embedded system (Schematic)                                      | . 46 |

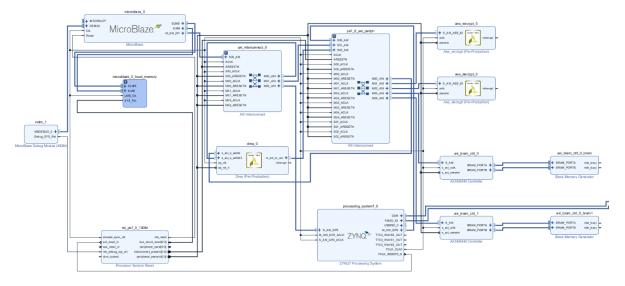

| Figure 26: A secure Embedded system (Architecture 1)                                 | . 47 |

| Figure 27: Logic ports from Synthesis                                                | . 48 |

| Figure 28: Utilization efficiency from Synthesis                                     | . 49 |

| Figure 29: FPGA target From Implementation                                           |      |

| Figure 30: Utilization efficiency from Implementation                                | . 49 |

| Figure 31: A secure Embedded system (Architecture 2)                                 | . 50 |

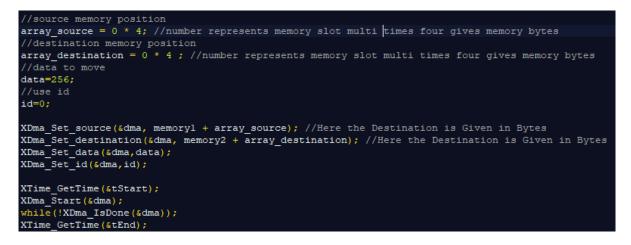

| Figure 32: Main operation, data copying                                              | . 51 |

| Figure 33: DMA Synthesis report                                                      | . 52 |

| Figure 34: DMA testing                                                               | . 52 |

| Figure 35: Setting the limits                                                        | . 53 |

| Figure 36: Testing the DMA                                                           | . 53 |

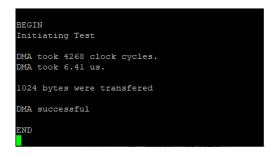

| Figure 37: Trasfer of 1KB                                                            | . 54 |

| Figure 38: Transfer time for different amount of data                                |      |

| Figure 39: Utilization and Performance estimation of AES encryption/decryption block | . 55 |

| Figure 40: Encryption & Decryption modules directives                                | . 55 |

| Figure 41: Connecting of the AES modules                                             | . 56 |

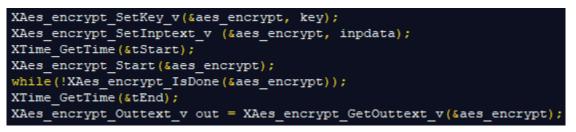

| Figure 42: Testing the AES encryption module                                         | . 56 |

| Figure 43: Testing the AES decryption module                                         |      |

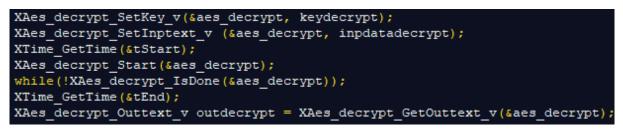

| Figure 44: Encryption and Decryption results                                         |      |

| Figure 45: Proof of Operation                                                        |      |

| Figure 46: Performance of Encryption and Decryption blocks                           | . 58 |

| Figure 47: Software implementation of AES code                                       |      |

| Figure 48: System Design                                   | . 59 |

|------------------------------------------------------------|------|

| Figure 49: HW Resources                                    | . 59 |

| Figure 50: A Random Number Generator                       | . 60 |

| Figure 51: Hardware encryption VS Software encryption (CC) | . 61 |

| Figure 52: Encryption and DMA transfer of 1KB              | . 62 |

| Figure 53:Encryption and Decryption                        | . 62 |

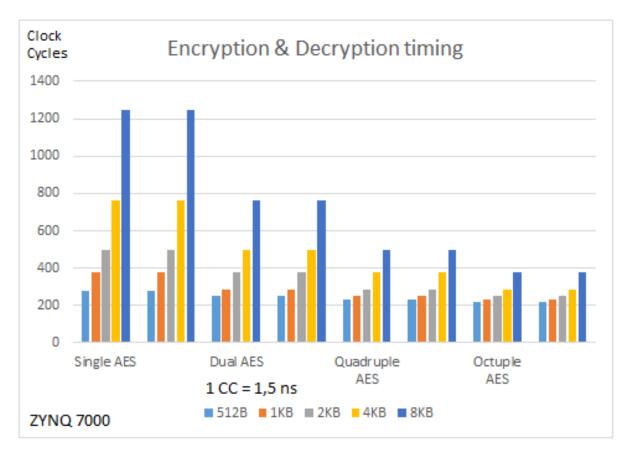

| Figure 54:Performance with multiple modules (clock cycles) | . 63 |

| Figure 55: Performance Graph                               |      |

## Acknowledgements

This thesis was prepared by the postgraduate student Kolimpianakis Filippos – George under the supervision of Professor George Kornaros. To Dr. Kornaros George I owe my sincere gratitude for his guidance and support throughout the processing of this Graduate Thesis.

#### 1. Introduction

An embedded system is a computer system with a dedicated function within a larger mechanical or electrical system, often with real-time computing constraints [54]. Embedded systems control many devices in common use today and ninety-eight percent of all microprocessors are manufactured as components of embedded systems [54]. Applications of embedded systems include smartphones, mp3 players, video game consoles, digital cameras, GPS receivers and technically every device that takes an input and can produce an output and functions as an independent system [54].

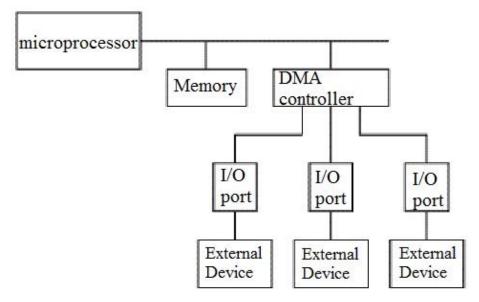

Direct Memory Access (DMA) is feature of computer hardware that allows devices to gain access to the main bus linking the processor to the system memory and move data directly between the main memory and another part of the system [57]. A dedicated DMA controller, often integrated in the processor, can be configured to move data between main memory and a range of subsystems, including another part of main memory [57].

Security and trusted operation of cyberphysical systems [59][64][65] is increasingly an important concern in modern digitalized, software-dominated internet-of-everything. Various techniques have been proposed to guarantee security for embedded devices, which focus to automotive systems and network communications [58][60][61][63] but also to protect internal execution of applications from faulty or malicious behavior [66][62].

#### 1.1 General

Many embedded systems have internal and external interfaces that produce or consume data [57]. These can be simple UARTs, external bus devices or complicated video and graphics devices [57]. A key part of any embedded system is ensuring that data flowing in to and out of these interfaces is handled properly and not lost or corrupted [57]. A simple way of moving the data between the peripheral device and main memory is to use the main processor to perform load or store operations for each byte or word of data to be moved [57]. The processor must wait for the peripheral to be ready before transferring each byte or word [57]. For many systems this is not a good use of processing time as the processor may be spending more time than necessary moving data between main memory and its external devices [57]. The alternative way is to set up a DMA transfer that gives the job of moving data to a special-purpose device in the system [57]. Once the processor has set up the transfer it can be occupied in his main task while the transfer is in progress or wait to be notified when the transfer has finished [57].

The obvious benefit of moving data using DMA transfers is that the processor can do something else while the transfer is in progress. However, using DMA sometimes has other advantages depending on the hardware involved [57]. These include:

**Data transformations** – applications targeted to video or digital signal processing, may be able to perform data transformations as part of the DMA transfer. These include byte-order changes and 2D block transfers [57]

**Lower power** – if the processor load is reduced and there are fewer interrupts it may be possible to run the processor at a lower clock rate or even to enter a low power mode while DMA transfers are in order [57].

**Higher data throughput** – a given processor may be able to handle more external interfaces at higher data rates, or a low-end processor might be able to handle more complicated interfaces such as Ethernet or USB [57].

The simplest is a known as a single-cycle DMA transfer and is typically used to transfer data between devices such as UARTs or audio codecs that produce or consume data a word at a time [57]. In this situation the peripheral device uses a control line to signal that it has data to transfer or requires new data. The DMA controller obtains access to the system bus, transfers the data, and then releases the bus. Access to the bus is granted when the processor, or another bus master, is not using the bus. [57].

Another type of transfer is a burst transfer. This is used to transfer a block of data in a series to the system bus. The transfer starts with a bus request; when this is granted, the data is transferred in bursts [57]. The burst size depends on the processor architecture and the peripheral, and may be programmable depending on the details of the hardware [57]. The last mode of operation is the transparent mode where the CPU never stops to execute its programs and the DMA controller transfer data free, but those programs do not use the system buses, so each party works on its own [68].

While a burst transaction is occurring, the processor will not be able to access the system bus. However, preventing the processor from accessing the system bus may cause a delay, which can reduce the system performance [57]. To minimize the effects of this problem, the DMA controller may release the bus after a fixed number of burst transactions or when a predetermined bandwidth limit has been reached. However, if the system needs to perform large DMA block transfers the system designer needs to carefully work out the bus bandwidth requirements to ensure there are no performance bottlenecks in the hardware or software design [57]. Before a DMA transfer can begin the processor must address the DMA controller the amount of data and the location to be moved. A DMA transfer usually has these attributes: **Source address -** the address from where the data is transferred, in main memory or the peripheral address space

**Destination address -** the address to where the data is transferred, in main memory or the peripheral address space

Transfer length - the overall length of the transfer, specified in terms of bytes or words.

Embedded system security is the reduction of vulnerabilities and protection against threats in software running on embedded devices. Like security in most IT fields, embedded system security involves a conscientious approach to hardware design and coding as well as added security software, an adherence to best practices and consultation with experts [55]. A DMA attack is a type of side channel attack in computer security, in which an attacker can penetrate a computer or other device, by exploiting the presence of high-speed expansion ports that permit direct memory access (DMA) [55].

Cryptography is about constructing and analyzing protocols that prevent third parties from reading private messages [56]. Various aspects in information security such as data confidentiality, data integrity, authentication, and non-repudiation are central to modern cryptography [56]. Modern cryptography exists at the intersection of the disciplines of mathematics, computer science, electrical engineering, communication science, and physics. Applications of cryptography include electronic commerce, chip-based payment cards, digital currencies, computer passwords, and military communications [56].

#### 1.2 Motivation

An embedded system controlling its peripheral devices and interfaces with the use of identification and permission-controlled DMA can provide the secure and reliable communication between memory and those peripheral devices. In addition, the use of light weight cryptography mechanism provides further more protection in a low-cost design and high-speed communication. One high performance DMA module with multiple channels and high throughput should provide the security needed through multiple AES hardware blocks designed and developed as a part of this thesis.

#### **1.3 Contribution**

The main contribution of this thesis is to design a DMA controller with permission rights for each device connected using embedded AES cryptographic hardware system for the transmitted data. As it will be demonstrated in the following sections, we develop such a system which provides a simple but reliable function in transmitting data between memory and peripheral devices in a high speed and low-cost design.

A device such as this can be used in a wide area of application. In medical applications for online patient monitoring (sensitive data and who can access it), in automotive for firmware update and memory data protection, smartphone or tablet memory protection mainly when accessing the internet, updating or installing new application, in surveillance system with camcorders with the use of id for data protection, in wave generation on real time operating systems and generally prevent malware attack. Those are some of the possibilities a system like this has to offer.

#### 1.4 Organization

The general approach of this work is to establish a secure protected DMA transmission between memory and peripheral devices on an embedded system with the use of hardware AES cryptography blocks. Both DMA controller and AES blocks are designed and developed as part of the work of this thesis. The remainder of this thesis is organized as follows:

- Chapter 2 states some Basic Principles

- Chapter 3 examines Embedded Systems Security

- Chapter 4 introduces a background on related work

- Chapter 5 analyzes the architecture and design methodology of the hardware and software infrastructure that has been developed

- Chapter 6 presents the performance results and analysis of the system developed as well as the comparison with the systems existing

- Chapter 7 concludes with the summary of this work and directions for future extensions

## 2. Basic Principles

Information security is the practice of protecting information and preventing unauthorized/inappropriate access, use, disclosure, disruption, deletion/destruction, corruption, modification, inspection, recording or devaluation of information, or at least reducing the chance of that happening [67]. The idea is to assure the authenticity, integrity, availability, confidentiality, non-repudiation of the data transmitted either when referring on Personal Computers, or in this case on Embedded systems [67] [3]. Security of embedded systems is creating a lot of issues because of poor security design as well as implementation and resource constraint [41].

Protection in Embedded systems is an important factor when in stage of designing of such systems. As explained in next chapter embedded systems like every device in personal computing has a lot of value Constrains, Vulnerabilities and Attacks, so in the stage of designing there has to be serious consideration in the methods to be used, cost of the embedded device as well as to the performance of the system expected. As observed in many cases the most of the attacks on an embedded device was targeting the DMA controller as the most data transfers origin from the specified controller. Some basic principles and architectures will be described in the sections following below.

#### 2.1 Embedded Systems

Features demanded in todays embedded systems include acceleration, flexibility, personalization, security, privacy, redundancy, scalability, modularity, root-of-trust, PUFbased keys, longer key sizes, etc. and especially in the case of multi-processor SoC (MPSoC) platforms and FPGAs [5]. Most of the SoCs nowadays use a security co-processor designed in register transistor level (RTL) on embedded systems developed for Smart grid uses sensors, monitoring, communications, automation and computers [6] A common application of coprocessors is the acceleration of cryptographic algorithms and gain speed. The purpose of designing such platforms is to improve the flexibility, security, reliability, efficiency, and safety of those systems [6]. The main idea when developing embedded systems is to achieve lower power consumption and lower design or manufacturing cost as much as possible but maintain user friendliness, feasibility and expandability [6].

Embedded devices transmit a large amount of sensitive data that include bank account numbers, passwords, social security numbers, medical records, etc. [7]. An attacker can develop malicious applications, thus, when installed on the device can obtain access to private sensitive information [7]. The best way to prevent these applications is to use anti-virus, anti-malware, and anti-spyware software which require a high amount of computational power and resources [7]; thus, the best way is to use cryptographic algorithms to protect sensitive data on SoC devices used in healthcare, home automation or automotive industry [13]. Embedded systems in automotive, healthcare and industrial control are progressively getting computationally efficient and network enabled, thus, security is becoming crucial for smart and intelligent systems built in these embedded systems [30] [41].

#### 2.2 Direct Memory Access

Direct Memory Access (DMA) is an attribute of Computer Systems for memory access and data transfer between memory and peripherals without the use of CPU [68]. The aim of DMA is to remove the load of the CPU so that it can be occupied with other operations. The processor initiates the DMA controller by sending the source address, Number of words and the destination address of data [53] [68]. Main advantages and modes of operation have been described in Chapter one so they will not be discussed further.

Figure 1: Typical DMA

As the use of DMA has become well known so has the large number of attacks on those controllers [69]. Direct memory access (DMA) protection is a necessity, especially in case of RAM memories where the most of accessible data that are currently being used by each device are located [69]. Penetrating a device from high speed ports that permit DMA is an important issue in embedded systems. Attackers use these ports to gain access to physical memory address space, acquire the devices purpose, steal data or cryptographic keys, install or run spyware and exploits or modify the system to allow backdoors or other malware [69].

#### 2.3 Cryptography

Modern cryptography depending on the key can be either symmetric (private key cryptography) or asymmetric (public key cryptography) [56]. In Symmetric-key cryptography both sender and receiver share the same key either if referring to Block ciphers, where inputs are in blocks, or stream ciphers, where inputs are individual characters [56]. Encryption and Decryption on symmetric algorithms use the same private key in each method. Most common private key algorithms are DES, 3-DES and AES (which is the one to be implemented in this thesis) [56]. In Asymmetric-key cryptography, sender and receiver use a pair of keys, a public key and a private key. Public-key algorithms are more computationally demanding because of the level of security they provide but are ideal for digital signature [56]. Most common algorithms are RSA, DSA and lately ECC (These is not going to be further reference thus it is not the topic of this thesis).

#### 2.3.1 Advanced Encryption Standard

The Advanced Encryption Standard (AES) originally known as Rijndael from its developers (Vincent Rijmen and Joan Daemen) is a symmetric cryptography algorithm (private key) block cipher with key sizes 128, 192 and 256 bits, so the same key is used for encryption and decryption [70]. AES operates on a two-dimensional table (4 x 4 array) of bytes called "*state*" and it takes 10 transformation rounds to convert the input, who is called plaintext, to the final output, who is called ciphertext, for a 128-bit key size, 12 rounds for 192-bit key size and 14 rounds for 256-bit key size [70].

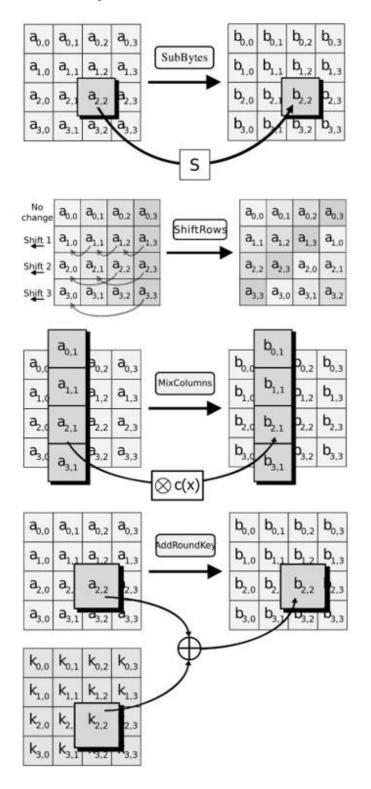

There are four steps of operation in each round of processing [70]. The first step is called "*SubBytes*" in which a 16 x 16 lookup table (substitution box or sbox) is used in order to find a replacement byte for every given byte of input [70]. In the second step called "*ShiftRows*" the rows of the table shift to left by zero, one, two and three according to the row [70]. The third step is "*MixColumns*" where each byte of a column is replaced of all the bytes in the same column, in particularly each byte in a column is replaced by two times that byte, plus three times the next byte, plus the byte that comes next, plus the byte that follows (the simplest way to explain the step) [70]. The final step is called "*AddRoundKey*" in which the round key is added to the output with the XOR logical operation [70]. The round key is computed in every round in which every Byte is replaced with another using the lookup table and the xor logical operation [70].

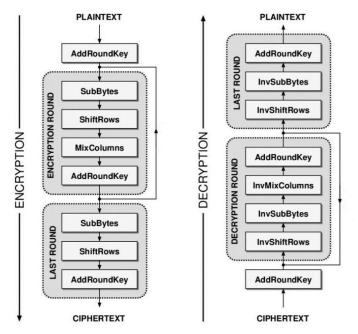

The four steps (which can be seen in figures below) explained in previous paragraph are executed in the order presented in every transformation round, except the last transformation round in which the "*MixColumns*" is not executed. This operation is for the encrypt mode of execution, during decryption mode inversive steps are executed in reverse mode of operation as it can be seen in detail in the figure below.

Figure 2: Steps of AES Encryption (Wikipedia)

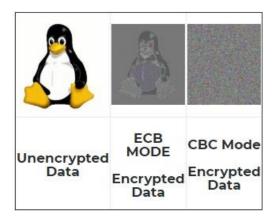

The "S-box substitution" is a non-linear transformation of two steps. First, the input bytes are multiplicative inversed and second, a transformation is applied [38]. S-box entries are implemented using look-up tables or computed mathematically [38]. Transformations "Shift-Rows" and "Mix-Columns" are linear operations [38]. The AES is a very widespread symmetric cryptography algorithm for encrypting data [38]. The AES algorithm has two modes of operation, the Electronic Codebook (ECB) mode and the Cipher Blocker Chaining (CBC) mode. The ECB mode in general is the main generation of AES in which each plaintext is encrypted as an independent block. In CBC mode each plaintext is XORed with the previous ciphertext so every block is dependent on the previous, thus, providing a higher level of security but consumes more time. The CBC mode was created because in ECB mode identical blocks produce the same ciphertexts, thus, it turns out to be a security risk. FPGAs in general offer the performance required to implement such an algorithm [38].

Figure 4: ECB vs CBC (Wikipedia)

#### 2.3.2 True Random Number Generator

For key generation often as a safe way to generate keys between parties often is used a hardware random number generator (HRNG) or true random number generator (TRNG). A TRNG is a device that generates random cryptographic keys to transmit data securely [71]. Most of the related work in the past use a TRNG to produce cryptographic keys [71].

#### 2.4 Xilinx Vivado

Vivado Design Suite is a development environment from Xilinx for system-level integration and implementation in order to design IP-centric SoCs. This software suite is produced for synthesis and analysis for hardware description language designs with a wide area of features including system on chip development and high-level synthesis analysis [72]. It is better conception compared to Xilinx ISE development kit, faster and more integrated [72]. This software suite is used in order to develop practical part of this thesis. The software consists of Vivado High-Level Synthesis (HLS), the Vivado Software and the Software Development Kit (SDK).

It is important to indicate that the communication protocol used between cores is the AXI4 interface protocol. Advanced eXtensible Interface (AXI) is a part of the ARM Advanced Microcontroller Bus Architecture (AMBA) with a parallel high-performance, synchronous, high-frequency, multi-master, multi-slave communication interface, mainly designed for on-chip communication [81]. AXI4 is the interface protocol used in the architecture of this project for all parties communication, from Microprocessors, IP blocks to peripheral devices and external ports.

#### 2.4.1 Vivado High Level Synthesis

Vivado HLS is a software tool included in the Vivado Development kit that accelerates IP creation to be used in SoCs. The idea is to create hardware modules in high level programming language like C, C++ and SystemC and the software after a successful synthesis exports RTL. The IP block exported is ready to be used in Vivado or ISE and can be used and reused many times. The software window is shown in the figure below.

Figure 5: Vivado HLS

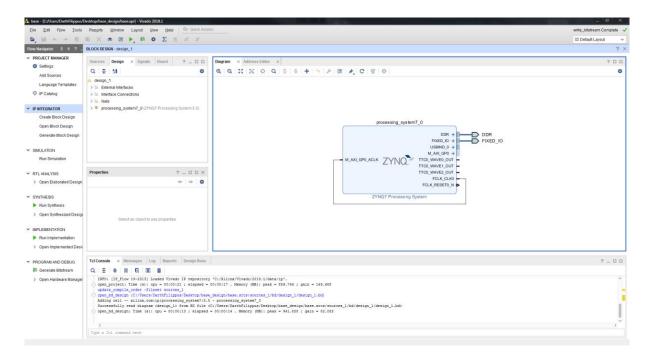

#### 2.4.2 Vivado

In the Vivado Software, IP Blocks can be added and connected in the AXI -4 interface. IP Blocks from the Vivado repository include processing modules, memories, interconnects, DSP systems, mathematical functions, bus interfaces, network functionalities and many more as well as IP Blocks created in Vivado HLS can be imported and used at will. After a design is validated by the software in can be synthesized. The synthesis function is the similar function as the compile function but in this case the Block Design is synthesized in logical ports that it will use in implementation.

After a successful synthesis follows the implementation stage where logical ports from the synthesis design are translated in an FPGA design in order to download it on a FPGA platform. It also places and routes the logical ports into device resources. In this case the FPGA platform to be used is the ZedBoard described in the next section. If the implementation is successful the bitstream file can be generated in order to program the FPGA target device. The software window can be seen in the section below.

Figure 6: Vivado Design Software

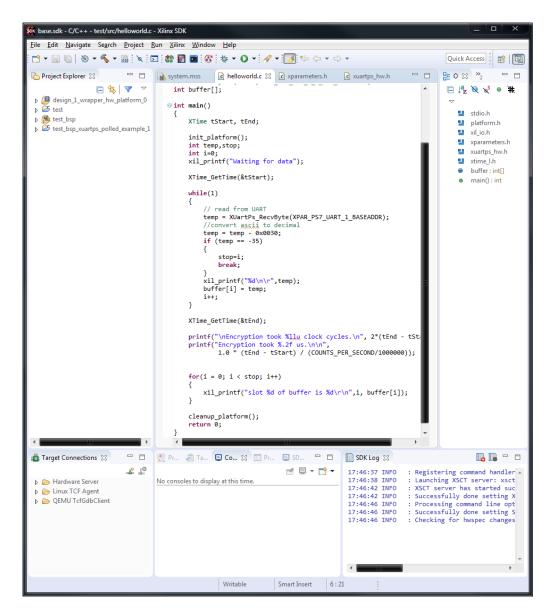

#### 2.4.3 Software Development Kit

The Xilinx Software Development Kit (SDK) is a software environment for creating applications for embedded systems on microprocessors like Zynq UltraScale+ MPSoC, Zynq-7000 SoCs and Microblaze. The SDK application offers multiprocessors designs, debugger and performance analysis. On this software program the applications are developed that is going to be run on the embedded device. Through this program the FPGA of the hardware target can be programmed and run the applications that are developed on the FPGA or the embedded microprocessor. The program is included in the Xilinx Vivado package and can be seen in the figure below.

Figure 7: Software Devepopment Kit

#### 2.5 ZedBoard

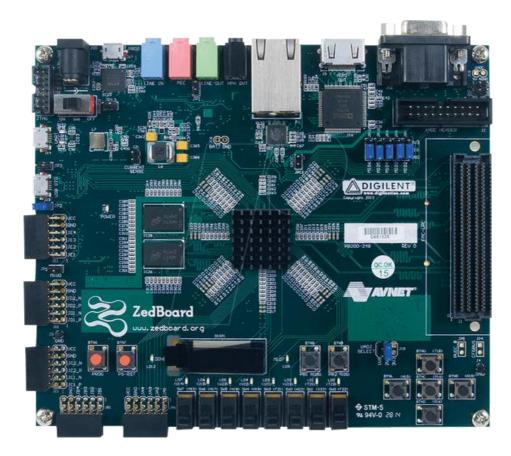

ZedBoard is a full development kit from AVNET that uses the Xilinx Zynq-7000 All Programmable SoC and supports a large area of applications. This is the FPGA hardware platform that is going to be used for this project so some of his features has to be mentioned. Features of the Zedboard include the Zynq – 7000 SoC processing system with ARM dual core processor A9 (677MHz max Frequency), 512 MB DDR3, 256 Mb Quad-SPI Flash, 4 GB SD card, Onboard USB-JTAG Programming 10/100/1000 Ethernet, USB OTG 2.0 and USB-UART, FMC-LPC connector (68 single-ended or 34 differential I/Os), 5 Pmod<sup>TM</sup> compatible headers (2x6), Agile Mixed Signaling (AMS) header, 33.33333 MHz clock source for PS, 100 MHz oscillator for PL, HDMI output supporting 1080p60 with 16-bit, YCbCr, 4:2:2 mode color, VGA output (12-bit resolution color), 128x32 OLED display, Onboard USB-JTAG interface, Xilinx Platform Cable JTAG connector, 8 user LEDs, 7 push buttons and 8 DIP switches. ZedBoard can be seen in the figure below.

Figure 8: Zedboard

## 3. Embedded Systems Security

Application of embedded systems can be found in in Automobiles, in Telecommunication to Motor and cruise control system, for Body or Engine safety, for Entertainment and multimedia in car, to E-Com and Mobile access, for Robotics in assembly line or Wireless communication [28]. Also, in Smart Cards, Missiles and Satellites for Security systems, Telephone and banking, Defense and aerospace or Communication [28]. In Peripherals and Computer Networking for Displays and Monitors, Networking Systems, Image Processing, Network cards and printers and in Consumer Electronics on Digital Cameras, Set top Boxes, High Definition TVs, DVDs [28]. All these applications have some constrains, vulnerabilities and attacks which are discussed in this chapter.

Most of the application above use a high-end processor for some real-time systems and integrate a DMA peripheral to handle the data transfers and the bus access [43]. The DMA reduces the power consumption it increases the CPU's bandwidth and frees up available processing capacity but more over the features of DMA are: a)Access to multiple peripherals in the processor, b)Multiple DMA channels in the processor, c)Different priorities for each channel, d)Handling the source and destination address, e)Handling the increment/ decrement of the source and destination address based on the configuration, f)Checking for the completion of the transfer of configured number of bytes for a DMA channel, g)Burst transfers which split the whole data transfer into multiple blocks and h)Generate an interrupt when required [44].

When designing secure embedded systems some factors has to be taken into consideration such as small form factor, good performance, low energy consumption (and, thus, longer battery life), and robustness to attacks [26]. Such attacks can include viruses, malwares, worms, physical tampering, and side-channel attacks [26]. Security engineering when developing intelligent devices like wireless phones, routers and switches, printers, SCADA (Supervisory Control and Data Acquisition) systems, electronic devices in cars and even medical devices has been an important aspect when users tend to manipulate them or harm then in any way [26]. Mileage counter manipulation, unauthorized chip tuning or tachometer spoofing has forever been a security risk [26]. Encryption has forever been computationally intensive and requires dedicated hardware in an environment where resources of the embedded system are restricted [26]. The design must meet the arrangements and the capacity as well as the cost of the embedded system. As attacks continue to increase, the development of countermeasures and the insurance of a secure execution environment (SEE) as well as the dynamic adaptation has to be a must have in embedded system security [26].

#### 3.1 Constrains, Vulnerabilities and Attacks

There have been observed and categorized 60,000 entries of Common Vulnerabilities and Exposures according to the survey in [29]. From these entries the authors have classified the attacks concerning embedded systems. In precondition class the requirements of the attacker include Internet facing device, Local or remote access to the device, Direct physical access to the device, Physically proximity of the attacker, Miscellaneous or Unknown [29]. For vulnerability they found Programming errors, Web based vulnerability, Weak access control or authentication, Improper use of cryptography and Unknown [29]. As far as the target concerned the hardware, firmware or OS and application [29]. For the attack methods they described Control hijacking attacks, Reverse engineering, Malware, Injecting crafted packets or input, Eavesdropping, Brute-force search attacks, Normal use and Unknown [29]. Last, as the effect of the attack they found Denial-of-Service, Code execution, Integrity violation, Information leakage, Illegitimate access, Financial loss, Degraded level of protection, Miscellaneous and Unknown [29].

On the overview of [30] the authors categorize the topics of embedded systems security. Some disadvantages in the nature of embedded systems include Limited processing power, Limited available power, Physical exposure, Remote and unmanned operation and limited network connectivity [30]. Some vulnerabilities Energy drainage (exhaustion attack), Physical intrusion (tampering), Network intrusion (malware attack), Information theft (privacy), Introduction of forged information (authenticity), Confusing/damaging of sensor or other peripherals, Thermal event (thermal virus or cooling system failure), Reprogramming of systems for other purposes (stealing) [30]. Typical attacks target at privacy authenticity, access control and confidentiality. The attacks can be physical, logical or side channel based. physical attacks include micro probing, reverse engineering and eavesdropping [30]. On the other hand, logical can be software based or cryptographic [30]. Some countermeasures against software attacks are based on architecture, on safe languages, static code analyzers, dynamic code analyzers, anomaly detection techniques, sandboxing or damage containment approaches, compiler support, library support and based on Operating system [30]. Countermeasures against side channel attacks are masking, window method, dummy instruction insertion, code/algorithm modification, balancing, etc. [30].

Survey [7] mentions existing defenses, both software and hardware based such as Software-based Mechanisms, watchdog checkers, Merkle trees, integrity trees, memory encryption, and modification of processor architecture. The paper categorizes the hardware attacks as Evil maid attack, Cold boot attack, Firewire DMA attack, Bus attack and software attacks as Buffer overflow attacks, Return-into-libc and Code injection attacks [7].

The developers in embedded systems had to use either software-based techniques or a coprocessor to achieve public-key cryptography. Software-based techniques are too computationally expensive for an 8-bit microcontroller. On the other hand, Coprocessor-based implementations need extra cost in hardware to support a single type of public-key cryptography [2]. Solution to that problem is the technique of reusable hardware, the share of computation units and the use of SRAM memory as cache [2]. One problem that arises is the level performance bottlenecks occurring from data transfers between the RAM and the coprocessor [2].

In medical field the physician uses embedded technology to acquire medical information about a patient where security is an important factor considering the doctor patient confidentiality [28]. With the use of embedded devices, the treatment of patients can be faster and more reliable. Application of embedded systems in medical field include Fetal Monitor, Oximeter, Defibrillator, Digital Flow Sensor, Pacemaker, Pulse oximeter, etc [28]. Types of these application can either be real time, standalone, networked or mobile in a small scale, medium scale or sophisticated [28].

IoT Sensor Devices and Automotive Electronic Control Units (ECUs) have a need for lightweight cryptography because they control critical functions as braking, acceleration etc. and are connected on a Controller Area Network (CAN) [40]. Those circuits have a need for Small code/area footprint, minimum latency and low power and that is the reason to use lightweight cryptography [40]. Automotive embedded Systems nowadays allow software installation, remote updates, data sharing, or application input data so software corruption has become a major concern [41].

Other protocols except the CAN in ECUs include Local Interconnect Network (LIN), FlexRay (for better rates of steering wheel and brakes), MOST (for multimedia) and Ethernet [51]. Every attack on these protocols target on Theft, Electronic tuning, Sabotage, Intellectual property theft, Privacy breach and Intellectual challenge [51]. Attacks can be categorized as Internal and Remote. Internal attacks include Vulnerabilities on the bus and Local attacks [51]. Remote include Indirect access (OBD port, CD player, USB port), Short range attacks (Wireless pairing of mobile devices, Car-to-car communications, Tire Pressure Monitoring System, Wireless unlocking), Long-range direct attacks (Telephony, Web browsing) and Long-range indirect attacks (App store, Side channel triggers) [51]. Constraints on automotive embedded systems contain Hardware constrains, real time, Autonomy, Physical constraints, Lifecycle and Compatibility constrains [51]. It is important when designing a secure communication architecture for internal or intervehicular communication to secure external communication [51]. Internal protections contain Cryptographic solutions, Solutions detecting anomalies in the system and Solutions to ensure integrity of the embedded software [51].

One literature survey [41] refers to attacks in Automotive Embedded systems. Lowlevel memory such as RAM, FLASH, and CACHEs are very important to ECUs and if an attacker manages to change the firmware, he can do serious damage to the entire system [41]. ECUs control and regulate information acquired by the sensors (Sensors convert physical quantitates to electrical signals and actuators to motion.) and there are 70 ECUs in one automobile with more than 100 million lines of code [41] [51]. Every memory in an ECU (flash and RAM) has a primary bootloader (PBL) and a secondary bootloader (SBL). PBL loads the application software from FLASH and the SBL loads from PBL, so every update that is to be made occur only on SBL [41]. It is important to have restrict access to the bootloader [42].

Features and characteristics of the automotive embedded system include limited processing power, limited power supply, physical exposure and network connectivity as written above in [26], same principles apply here [41]. Threats identified as Energy drainage (exhaustion attack), Physical intrusion (tampering), Network intrusion (malware attack), Introduction of forged information (authenticity), Confusing/damaging of sensor or other peripherals, Reprogramming of systems for other purposes (stealing) [41] [53]. Vulnerabilities in embedded systems have been discussed previously but as far as automotive is concerned are Programming errors, Network based vulnerability, Weak access control or authentication, Improper use of cryptography [29] [41]. Requirement for the attacker are Internet facing device, Local or remote access to the device, Direct physical access to the device, Physically proximity of the attacker and general attacking strategies on memories [30] [41].

Attacks can be classified as physical, logical and side channel attacks [30], [41]. Physical include Reverse engineering, Micro-probing, Eavesdropping and memory access Using Debuggers [30] [41] [42]. Logical refer to Code injection attacks (Stack based buffer overflow, Heap based buffer overflow, Shell code injection, return to libc attack, Return oriented programming), Cryptographic attack (Brute forcing, Dictionary attack) [30] [41] [42]. Last side channel attacks are based on Fault injection attacks, Timing analysis attack, Power analysis attack and DMA attacks [30] [41].

Wireless sensor nodes and RFID tags are very efficient devices that consume small amount of power and require little area. The substantial security, the performance of those devices as well as the minimum storage space and computational capability are the reason, we implement Light Weight Cryptography algorithms. Those algorithms have certain features. They process at low power consumption, low communication cost, low area, low energy and small processing time [1]. For security in Smartphones, tablets, medical implants and wireless sensor networks, that lack resources and power consumption a lightweight stream cipher is proposed in [1], [3].

### 4. Background on Related Work

Some important projects on embedded systems to provide security on applications that were discussed in the previous chapter are presented in brief in this one. One processor system with a general-purpose processor with a cryptographic processor that performs cryptographic operations and enforces security on critical parameters should prevent exposure of critical security parameters outside the cryptographic processor and implements a limited Scripting engine to provide highly efficient security [52].

A hardware-based Montgomery multiplier, and pairing software is proposed in [3] but lack in some sections. a) Session keys must be embedded in each node at initial implementation, b) Use of a single session key at multiple nodes requires synchronization; and c) Digital signatures are not possible, since all nodes share the session key [3]. It also shows the increase of power and energy consumption. The design uses optimizations for Miller loop, final exponentiation, and Elliptic Curve Cryptography (ECC) operations. It was designed in VHDL and runs in an ARM Cortex-A9 processor [3].

Demands for security in Embedded Systems is increased every day. In [2] the authors propose cost-efficient hardware that can compute the public-key cryptography with the use of a coprocessor that supports both RSA (range from 256 bit to 2048 bit) and Elliptic Curve Cryptography (ECC). They also propose a small direct memory access (DMA) to remove system-level performance bottlenecks and transfer data between coprocessor and external RAM in order to make full use of the coprocessor [2].

A hardware-software co-design of RSA is analyzed in [35] where hardware accelerators are providing the highest performance but fail in flexibility and adaptability to changing algorithms, parameters, and key sizes. The authors estimate that they combine software and hardware that offer high performance and the advantage of low-power and low energy consumption [35]. Test of this design was performed on the Xilinx Zynq- 7000 SoC platform, which integrates a dual-core ARM CortexA9 processing system and the RELIC library (Efficient Library for Cryptography) was used. They show the speed up of the co-design vs the pure software implementation of the RSA algorithm that run on the same platform [35]. An RSA implementation for system on programmable chip (SoPC) can be investigated in [37]. The use of the RSA processor is believed to be at low cost, more flexible and high performance when implemented in a FPGA platform [37]. It is a hardware/software integration of RSA in verilog HDL language and was tested on an Altera Cyclone II FPGA [37]

One cryptographic processor for security in embedded systems is proposed in [4] named CryptoAeg. In difference from general SoC-based solutions, CryptoAeg has its own cryptographic instructions to accelerate cryptographic processing by eliminating the need of coprocessors and minimize the cost of the system for the use of RSA or ECC [4]. The design relies on the ALU architecture without including a multiplier in order to reduce the hardware cost and complexity of software program [4]. It provides security for portable devices and wireless communications [4].

Public key encryption algorithms are very cost efficient when used in wireless sensor nodes, yet if necessary, the best to use is Elliptic Curve Cryptography (ECC) for short keys [24]. Public-key algorithms are more computation-intensive than other types of crypto algorithms like symmetric-key algorithms and hash functions, but are an importance when talking about digital signature and authentication [24]. The performance of the ECC is tested on DSP and it shows efficient results, although it does not run on a general-purpose processor but hardware features of DSP to accelerate the ECC operations are used for this reason [24]. Same in [25], a three side-channel protected hardware/software co-design for a small but particularly fast pairing-based cryptography in a stand-alone microprocessor seems to be another good option when referring to embedded applications because of the low chip area needed. With an assembly optimized software implementation, the low area requirement and the high runtime of pairing-based cryptography the option is viable in interactive embedded applications when involving wireless sensor networks [25].

Elliptic Curve Cryptography for MSP430-Based Wireless Sensor Nodes is a new energy save architecture, a dedicated hardware module for area and speed-optimized software solution [32]. It uses 4kGE of dedicated chip area and consumes less energy but the efficiency of the algorithm in speed is the same as before [32]. One hardware/software Co-design of Elliptic Curve Cryptography is provided in [34] for the 8051 Microcontroller. It uses a minimalist hardware accelerator for ECC and a dedicated interface with direct memory access for better performance and reduction of hardware cost in comparison with previous work on similar 8-bit platforms [34].

Nowadays, an electronic computational unit is embedding more data and power management in connected, autonomous and electric vehicles [5]. The authors in [5] refer to a Reconfigurable hardware technology combined with static multicore processors and memory into a SoC for embedded cryptosystems. Their work focuses on the HW/SW co-design of a secure automotive computation unit which is composed of a full post-quantum cryptosystem implemented in programmable logic to prevent intruder's decryption using quantum computers

[5]. To achieve this, they implemented the McEliece algorithm, a true random number generator, the advanced encryption standard and a secure hash algorithm. They used the Zynq UltraScale+ MPSoC ZCU102 evaluation board to test their design.

In [6] the authors propose a security coprocessor with the general-purpose processor in an AMBA bus and an AXI interface in a MPSoC. SM2 asymmetric encryption algorithm and SM3 hash function is used to ensure the security in the system [6]. The accelerator in the security coprocessor mainly executes computational functions like Modular multiplication and modular addition. This SoC could be used in a power distribution network as a smart control terminal or a smart metering and power quality analysis instrument [6].

The authors in [10] propose a cryptographic accelerator to multiple cryptographic tasks for Internet Protocol security (IPsec) by using a Dynamically Reconfigurable Processor (DRP) from NEC electronics in a SoC with the embedded processor. The accelerator provides highthroughput cryptographies, cost efficiency, and high flexibility to embedded systems and presents a practical solution to optimize cost, performance, and power consumption [10]. With the use of Virtual Hardware and Run-Time Configuration based on Double Buffer the simulation results show that co-processing system eliminates a bottleneck of the software execution and achieves performance improvement [10].

As technology rises the authors in [13] present a 65 nm Fulmine secure data analytics System-on-Chip for IoT end-nodes with Convolutional Neural Networks and computer vision. This SoC provides full programmability, low-effort data exchange between processing engines, high speed, and low energy. By combining cores and accelerators within a single tightlycoupled cluster this SoC improves time and energy in a simple software solution with flexibility, high security and sensible budget [13].

A great idea is provided in [15] where the authors make use of a dedicated DMA controller, which encrypts and decrypts data in every transaction according to the function required. The Advanced Encryption Data is used to transform data in each DMA request, that prevents transmitted data to be hacked by an unauthorized user [15]. The idea was developed for the IPhone of Apple Computers but can work for every embedded device. Another great idea presents in [16] where each I/O controller has its own identifier and every identifier its own encryption key. Whenever a DMA transaction is to be performed, a computing device called the cryptographic engine protects the data according to the identifier of the I/O controller [16]. The cryptographic engine has an identifier table with the cryptographic keys of every I/O controller [16]. According to the device id, the cryptographic engine encrypts with a different key every time a DMA request is to be made [16].

Same idea for DMA security developed in [19] with the use of an encryption/decryption unit in the DMA path. For historical reasons the idea that presented in [20] explains the scenario of using a security module for encrypting and decrypting data whenever a DMA request is made [20]. Every encryption or decryption is established through the DMA controller without disturbing the main processor [20]. This scenario was proposed for personal computing but applies still in embedded systems applications. In [22] the authors develop a high-performance DMA design with four channels able to transfer 1.6 megabytes of data every second. This DMA controller uses the advanced microcontroller bus architecture (AMBA) and was implemented in Verilog HDL [22].

One implementation of all three AES algorithms (AES-128, AES-192 and AES-256) can be investigated in [23] using cryptographic accelerator with both ECB and CBC mode as well as SHA-1 and SHA-256 hash algorithms combining the speed of hardware with the flexibility of software. The Sboxes in this implementation are in RAM blocks in order to increase the throughput [23]. The hardware cryptographic accelerator using FPGA technology and the client application was tested in a linux platform on a PC using PCI Express interface [23]. In order to achieve higher computation speed, flexibility and implementation scalability parallelization mechanisms were used for all encryption and hash blocks [23]. A kernel driver was also developed in order to connect the hardware unit to the PC and acquire direct access operations to the hardware resources required by the multitasking environment [23].

One Hardware-Software co-design of Cellular Automata Cryptosystem (CAC) shows experimental results better than DES and comparable to AES [18]. CAC is supposed to be fast in execution because of its small code size, designed for embedded systems with an acceptable level of security [18]. CAC is written in verilog and was acceptable by the time invented because of its simplicity (only four levels of transforms) and the level of security that provides, but obsolete nowadays.

According to the authors of [31], a hardware acceleration of AES Cryptographic Algorithm can be developed for IPSec, to provide secure data at the IP layer but the drawback is that itneeds a lot of computational power. It uses a hardware acceleration of AES ECB and the goal was to secure speed and energy efficiency [31]. They tested it on Xilinx Virtex-6 ML605 on 250 MHz and they achieved 391.25 Mbps throughput [31].

An advanced bus architecture for embedded systems that use AES encryption to improve performance and possibilities is provided in [8], called CDBUS. The benefits using the CDBUS include a) low cost and low pawer control bus, b) dual bus structure, c) high – throughput data bus, d) high - efficient DMA with dynamic arbitration, e) high – performance

AES transfer mode [8]. A testbed provided in [9] shows results for execution of various sha3 algorithms. Those results include a) hardware execution time, b) software execution time, c) HW/SW speed up and d) maximum clock frequency. Results were obtained using vivado design Suite. In [11] is an example of a multi FPGA SoC with 24 microblade performing parallel and pipelined signal processing applications in embedded system to achieve performance and [12] shows an improved DMA controller to boost high speed data transfer in MPU based SOC.

One cryptography co-processor in NoC systems can offer complete functionality with just an integrated DMA, embedded key registers, command priority queues, and AES counter mode of operation (CTR) [36]. The general-purpose processor (GPP) only requests encryption and decryption operations from the co-processor. The scenario proposed is high-performance pipelined AES core with counter mode of operation (CTR) with an integrated DMA module to take the load off the GPP and perform all the cryptographic tasks and data transfers in a scalable NoC design [36]. They used an integrated AES core from Opencores with key register file in our tile to store keys and the priority command queue [36]. The design was only tested in modelsim and it was estimated to be 230 times faster than the pure software implementation of the same algorithm [36].

Two approaches are presented in [38] to implement the AES encryption algorithm in a multi-processor SoC (MPSoC). The first one is composed of a Network Interface (NI), a Controller, AES and internal memory and for the second, a Network Interface, a plasma processor, AES, Direct Memory Access (DMA) and internal memory [38]. The cost to design a pipelined AES algorithm in FPGA is very low and it provides resource utilization, high speed and high throughput [38]. They developed this design in VHDL with the use of the AXIM platform and the customized AES based crypto module and was tested with modelsim and Virtex6 ML605 from Xilinx [38]. In the first approach the design uses less hardware resources and achieves better performance than the second approach but in both cases the latency has reduced significantly [38].

Constant growth of data transfer requirements in modern embedded systems made the need to implement the AES256 and TDES as hardware IP cores on FPGA platform with the use of AXI interface [39]. This way the performance of data encryption/decryption is approximately 13 to 416 times faster compared to the pure software implementation of the algorithms and in addition takes the offload of the main processor [39]. The results are comparable to modern Intel processors with specific instruction set [39]. The IP cores are modeled in VHDL and tested on a zedboard.

The Maestro architecture described in [43] is a hardware/software co-design with two components, one processor for system initialization and control and the hardware AES core for high performance AES encryption/decryption. The design reaches a very high throughput, through a tightly coupled encryption and round key generation units in encryption unit and ahead of time round key generation in decryption unit [43]. The ten-stage pipelined architecture was considered for the AES engine and the authors believe that it can encrypt or decrypt one block of data in one clock cycle [43]. It is also believed to be cost efficient considering the high throughput. The Altera DE2-115 development and educational FPGA board was used to test this design which includes the Nios II core, Avalon interconnects, SRAM, SDRAM and on chip memory [43].

A secure communication protocol is described in [46] in which cryptographic coprocessors are used and the cryptographic key is computed according to a password that was set between the users. The hardware/software co-design uses AES-256 block cipher, is used in real time applications and is supposed to be cost-efficient, high power and high secure hardware structure [46]. It provides high security, portability and speed at low costs [46]. The design was tested in Linux OS on a ZYBO combining the ARM CPU and the FPGA [46].

There are three ways to connect a security module to the embedded processor, a) in the processors Datapath, b) through the internal register file of the processor and c) access through the peripheral bus as a peripheral [47]. An AES-128 security module is implemented on [47] as an IP-Core with a true random number generator (TRNG) for keys and is tested in different platforms [47].

One scenario that a Co-processor can be used in some area of application such as random number generation or hash generation and error correction is applied in [21]. The Co-processor performs forward error correction using BCH and Reed Muller algorithms IP Blocks and SHA-1 IP Block for hash generation in embedded systems [21]. The CP is modeled using Verilog HDL and tested with Altera-Acex FPGA [21].

The main goal when referring to security in essence is a vault manager to protect the firmware if an embedded device from unauthorized access [27]. The authors in [27] propose a hardware vault such as this which includes of a shadow RAM or shadow Cache, flash memory, and a vault manager. The architecture proposed offers good security with a small performance penalty over OS applications [27]. The key points of this architecture include a) the vault is external to the processor, b) assures instruction integrity and c) provides trust on firmware upgrades [27].

In [14] the authors implement a hypervisor named BitVisor with minimized code and a parapass-through driver for ensuring storage encryption in ATA input/output devices. It is designed for virtual machine monitors and mainly for desktop operating systems [14]. Similar in [17] a hardware encryption module in the processor 's memory access path is used by the processor to secure information. Same as before used mostly for hypervisor and virtual machines. In this work the security module is an application specific integrated circuit (ASIC), a general-purpose processor on field programmable gate array (FPGA), designed and configured to perform security operations for the processing system [17]. Another bare-metal hypervisor running on virtual machine OS is the Silvermont microarchitecture for Intel x86 processors, running Windows is proposed in [33] but it is mainly used in POS machines and industrial embedded devices.

For secure mobile authentication a new architecture is presented to produce cryptographic keys and values for use inside an Enhanced Cryptographic Engine (ECE) [48]. A software Application Programming Interface provide stronger security for commands and data and a software emulator ensures secure communication between multiple computers and mobile devices [48]. A Trusted Execution Environment (TEE) provides secure modification, removal and update on embedded systems used in Automotive or health-care networks [48].

Securing DMA transfers can be also accomplished through virtualization based on hardware/software and provide high security with a formal verification of isolation and availability and a low performance overhead [49]. One software-based parallel cryptographic solution with a parallel memory embedded SIMD matrix processor is proposed in [50] which executes encrypting and decrypting cryptographic algorithms. The architecture is very effective for private information protection that promises low power and small chip area consumption and is intergraded in real time [50].

The contribution in [45] presents one hardware solution for ensuring microcomputer bus systems through a Tree Parity Machine Rekeying Architecture (TPMRA). The TPMRA IPcore is designed for adaptability, low cost terms, variable bus performance requirements, authentication of different bus participants as well as the encryption of chip-to-chip buses [45]. A co-processor module together with an application software encrypts communications between CPU, memory and other hardware through stream cipher techniques, Tree Parity Machine together with a hash algorithm that acts as a key stream generator for authenticated key exchange in AMBA bus system [45]. The design was written in VHDL and tested on a FPGA demonstration system, consisting of several FPGA boards [45].

## 5. Design and Architecture

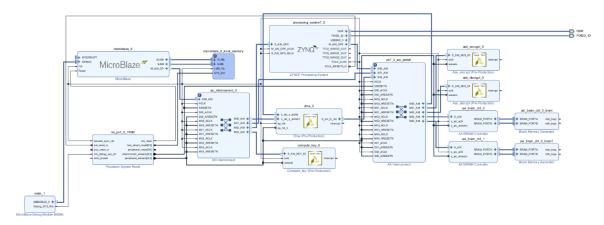

In this chapter we describe the architecture and design methodology of the hardware and software infrastructure of the project developed. The important characteristics of an embedded system are speed, size, power, security, integrity, authenticity, reliability, accuracy, adaptability, functionality, cost, power requirements, size and weight. In this project a secure DMA controller is been developed with the additional AES block cipher technique for extended security. DMA controller is developed in high Level Synthesis the execution of which is successful under certain constraints. Different IDs are used for every peripheral on the embedded device with different permissions for every ID for write or read operations.

A successful data transfer over DMA depends on the permissions set by the cryptographic co-processor with the addition of AES encryption on those data for secure transmission. Encryption keys are set by the same cryptographic coprocessor in the beginning of the session using a true random number generator. When a data transfer on the embedded device is in order, according to the ID and the permissions granted, the data will be encrypted and decrypted in the other end by AES IP-Blocks also developed in High Level Synthesis in the purposes of this thesis. The design is explained in detail in the sections following.

#### 5.1 DMA Controller

DMA transfers are used for fast data transfer between the IP core or processor and the system memory or the peripherals. In this particular project the DMA is used to transfer secure encrypted data from the cryptographic module to the peripheral or memory that are destined. The end device then uses the key that is provided by the cryptographic co-processor to decrypt the transferred data. The DMA controller has been developed with the Vivado High Level Synthesis (HLS) tool with the use of C programming language, thus, creating an IP block that is used to transfer secure data though the peripherals.

Every peripheral in this design uses a unique device ID for the purposes of communication with other peripherals. The architecture of our DMA controller is designed to receive certain arguments in order to execute a successful DMA transfer. Those arguments are the read and write position of each memory, the quantity of data to be transferred and the ID number for each device. Some boundaries have to be made considering every device ID, because as explained before every device has different rights and permissions. Those boundaries are inserted from a channel as arguments different than the channel we use for the main arguments and is operated exclusively by the cryptographic co-processor.

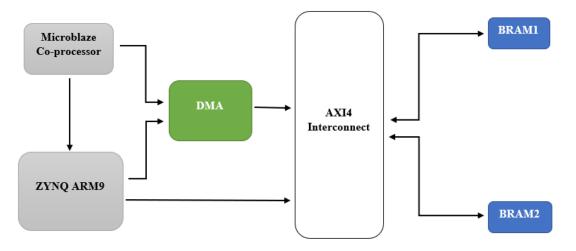

The cryptographic co-processor is a Microblaze microprocessor used as a shadow in this design which delivers the cryptographic keys to CPU, memory and peripheral devices and sets the arguments-boundaries for each of those devices according to the device ID. After that, every other main process or data transfer is performed by the main CPU, the ZYNQ processing system that includes the ARM 9 two core microprocessor. A main schematic of this project can be shown below.

As it can be seen the figure above the AXI-4 environment interface protocol is used for the communication between CPU, memory and peripherals. The DMA IP block has two channels, one for the boundaries provided by the Microblaze microprocessor and the second for the main arguments of the application. Two BRAMs are used in this case scenario in order to test the liability of the system. As the systems boots the application running on the microblaze applies the restrictions on the DMA module and after that, every DMA transfer requested by the applications running on the ARM9 has to apply to those restrictions. The BRAMs are just used as to transfer data from one to the other according on the boundaries given from the microblaze.

The architecture of the design will be explained in more detail, in the sections below. As mentioned Vivado High Level Synthesis is used to build this DMA controller module. As a start the two channels have to be separated, one for the boundaries and one for the main arguments. This is a very sensitive directive as it controls who has rights to use this channel and who doesn't and has been made clear who is supposed to do what. DMA is designed with a master AXI port to associate with the peripheral devices and two AXI slave ports, one for the communication with the microblaze and one for ARM9. The channels can be seen in the pictures bellow.

| HLS | INTERFACE | s_axilite | port=source bundle=s_axilite                 |

|-----|-----------|-----------|----------------------------------------------|

| HLS | INTERFACE | s_axilite | <pre>port=destination bundle=s_axilite</pre> |

| HLS | INTERFACE | s_axilite | port=data bundle=s_axilite                   |

| HLS | INTERFACE | s_axilite | port=id bundle=s_axilite                     |

Figure 10: Main arguments (ARM9)

| HLS INTERFACE | s_axilite | <pre>port=source_limit_begin bundle=s_axilite2</pre>      |

|---------------|-----------|-----------------------------------------------------------|

| HLS INTERFACE | s_axilite | port=source_limit_end_bundle=s_axilite2                   |

| HLS INTERFACE | s_axilite | <pre>port=destination_limit_begin bundle=s_axilite2</pre> |

| HLS INTERFACE | s_axilite | <pre>port=destination_limit_end bundle=s_axilite2</pre>   |

Figure 11: Boundaries Channel (Microblaze)

| int dma( volat: | ile int *memory,                                    |

|-----------------|-----------------------------------------------------|

|                 | unsigned int source,                                |

|                 | unsigned int destination,                           |

|                 | unsigned int data,                                  |

|                 | unsigned int base address source,                   |

|                 | unsigned int base address destination,              |

|                 | unsigned int id,                                    |

|                 | unsigned int source limit begin[4],                 |

|                 | unsigned int source limit end[4],                   |

|                 | unsigned int destination limit begin[4],            |

|                 | <pre>unsigned int destination_limit_end[4]) {</pre> |

Figure 12: Ports of DMA

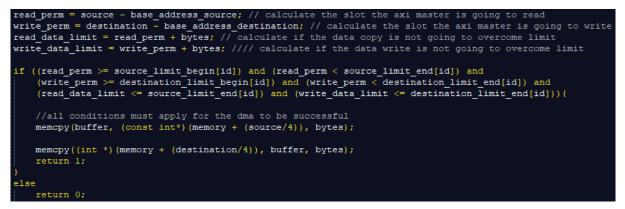

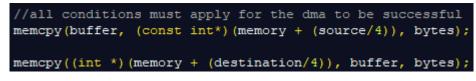

The functionality of the specific design of DMA depends on the ports shown above. Once the boundaries of the application have been inserted and the main application starts, if a DMA transfer request occurs, the algorithm calculates if the source and destination limits are exceeded. A successful DMA depends whether or not these limits are exceeded. A part of this algorithm written in C Language is shown next.

Figure 13: Calculating the Limits Source and Destination

One benefit arises from this architecture, the use of IDs provides device authentication in the system, so that no other party can use the same channel. The advantage of using priorities for those IDs make it even a stronger security mechanism. After a successful Synthesis, a Register Transistor Level (RTL) IP Block is exported in order to be used in the general design of this project in Vivado. The security is provided by the hardware, while the memory permissions for each ID are given by one of the applications running over the hardware. In each call for a DMA execution the main application inserts the user's ID, the memory location of the BRAM memory that is going to read, the location of the BRAM memory that is going to write, as well as the quantity of the data to be moved as arguments to the DMA block. If the permissions being set for the certain ID are valid and do not exceed the memory limits for the two BRAM data will be successfully moved. In other case DMA will fail due to denied access (read/write) on one or both BRAMs.

While it is strange to connect two BRAMs in the same AXI master channel and not use two it is perfectly explainable. Direct copy from source memory to destination memory is not permitted so we have to use a buffer in our architecture. Data are firstly copied to the buffer and then from the buffer to the destination, so a second AXI master channel is a waste of space. The AXI interconnect we use is to connect the two BRAMs to one AXI master channel as well as to prevent timing issues.

DMA controller has been designed in a way that every data transfer between two BRAMs can be accomplished only under certain conditions and that's the reason these restrictions cannot be exceeded. The DMA restrictions are accomplished straight on the hardware design of DMA block that is responsible to perform data transfers and without the initialization of these restrictions every call for DMA transfer will be a failure.

#### **5.2 AES IP-Blocks**

Embedded systems have sufficient resources such as memory, power and size, thus, they are not able to provide most of the existing cryptographic algorithmic codes. In this section **Lightweight Cryptography** is developed for those devices. Secure processing in this design is accomplished with an embedded cryptographic unit. AES security cryptographic algorithm was chosen for this particular project for its simplicity and the level of security that provides. Two modules created to encrypt and decrypt data, one for encryption and one for decryption algorithm. The reason the two modules are developed separate is to avoid using more chip area than is necessary. Data are encrypted in the one end and decrypted in the other end by different encryption/decryption modules. In that way a higher level of security and integrity is achieved.

#### 5.2.1 AES Encryption Module

A straight-forward implementation of the AES cryptographic algorithm is used on this project developed at Computer Science Department from University of Santa Barbara (<u>http://cs.ucsb.edu/~koc/cs178/projects/JT/avr\_aes.html</u>). It was selected because it is a simple implementation of the AES and the authors of it have given permission to use, copy, modify and distribute of this code for any purpose. In order to use this code as a hardware module, changes have to be made in the code. All details and changes are been explained as follows.

The Advanced Encryption Standard, as explained in Chapter 2, has four steps of operations. All steps are executed in the order they are described except the last transformation where the ""*MixColumns*" is not executed. These four steps are analyzed in C-code.

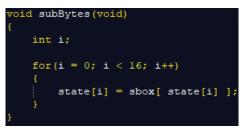

#### 5.2.1.1 SubBytes

Replacement of the byte in every given byte of input from the lookup table (sbox).

Figure 14: SubBytes in C-code

#### 5.2.1.2 ShiftRows

The rows of the table shift to the left.

```

void shiftRows(void)

{

byte temp;

//Row 2

temp = state[1]; state[1] = state[5]; state[5] = state[9];

state[9] = state[13]; state[13] = temp;

//Row 3

temp = state[10]; state[10] = state[2]; state[2] = temp;

temp = state[14]; state[14] = state[6]; state[6] = temp;

//Row 4

temp = state[3]; state[3] = state[15]; state[15] = state[11];

state[11] = state[7]; state[7] = temp;

}

```

Figure 15: ShiftRows in C-code

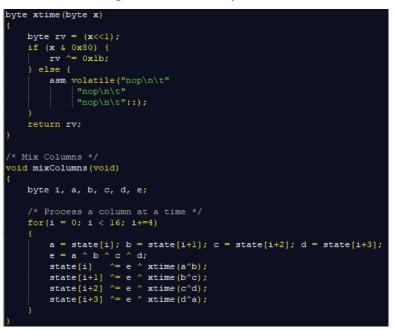

#### 5.2.1.3 MixColums

Each byte of a column is replaced of all the bytes in the same column.

Figure 16: MixColums in C-code

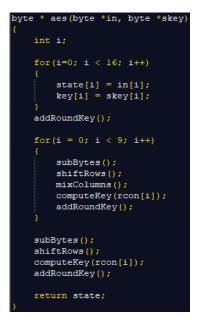

### 5.2.1.4 AddRoundKey

The round key is computed in every round, in which every Byte is replaced with another using the lookup table and the XOR logical operation.

| void c  | omputeKey(byte                 | rcon)   |

|---------|--------------------------------|---------|

| 0       |                                |         |

|         | te buf0, bufl,                 |         |

|         | 0 = sbox[ key                  |         |

|         | <pre>fl = sbox[ key</pre>      |         |

|         | 2 = sbox[ key                  |         |

| bu      | <pre>t3 = sbox[ key</pre>      | [12] ]; |

|         | (0) ^= buf0 ^                  | rcon;   |

|         | [1] ^= bufl;                   |         |

|         | (2) ^= buf2;                   |         |

| ke      | /[3] ^= buf3;                  |         |

|         | (4) *= key(0)                  |         |

| ke      | /[5] ^= key[1]                 |         |

|         | /[6] ^= key[2]                 |         |

| ke      | /[7] ^= key[3]                 |         |

| ke      | /[8] ~= key[4<br>/[9] ~= key[5 | 1:      |

| ke      | (9) *= key[5                   | 17      |

| ke      | /[10] *= key[6                 | 12      |

| ke      | /[11] *= key[7                 | 17      |

| ke      | [12] *= key[8                  | 19      |

| ke      | [13] *= key[9                  | 12      |

| ke      | /[14] *= key[1                 | 01;     |

| ke      | /[15] *= key[1                 | 1);     |

|         |                                |         |

| void ad | idRoundKey (voi                | d)      |

| in      | 17                             |         |

| for     | (1=0; 1 < 16;                  |         |

|         | state[i] ^=                    | key[i]; |

Figure 17: AddRoundKey in C-code

Figure 18: Main function to produce the ciphertext

Figure 19: Changes made in order to synthesize a Hardware IP Block

#### 5.2.2 AES Decryption Module

On the AES Decryption Algorithm inversive steps are executed in the reverse mode operation. The C-code for this implementation did not actually exist so it had to be reverse engineered from the Encryption C-code. The inversive steps and the main operation of the AES decryption mode are shown below. Again, all steps are executed in the order they are described except the last transformation where the ""*MixColumnInv*" is not executed.

#### 5.2.2.1 AddRoundKey

The round key is computed in every round in which every Byte is replaced with another using the lookup table and the XOR logical operation.

| void | 1 0 | O.BMP | *** | •¥       |     | Tnu        | the | rt e | -   | 207         | 1   |     |   |

|------|-----|-------|-----|----------|-----|------------|-----|------|-----|-------------|-----|-----|---|

| {    | 1 0 | omb   | uc  | en       | ey. | TUA        | (P) | fre  | -   | 001         | *   |     |   |