HAΕΚΤΡΟΝΙΚΑ ΣΥΣΤΗΜΑΤΑ ΤΗΛΕΠΙΚΟΙΝΩΝΙΩΝ & AYTOMATIΣΜΟΥ (TeleAutoS)

# ΔΙΠΛΩΜΑΤΙΚΉ ΕΡΓΑΣΙΑ ----- THESIS -----

# MEDIBERRY

Automatic ME dication DI spenser using Rasp BERRY Pi

Ονοματεπώνυμο: Αντώνιος Ι. Ζερβουδάκης

Εισηγητής: Δρ. Αντώνιος Κωνσταντάρας

(c) 2020

# Ευχαριστίες:

Σε αυτό το σημείο θα ήθελα να ευχαριστήσω:

- Πρώτα την γυναίκα μου Γεωργία και τα παιδιά μου Γιάννη και Στέλιο που έκαναν τόσο καιρό υπομονή για να ολοκληρώσω το Μεταπτυχιακό αυτό.

- Τους γονείς μου που με μεγαλώσανε και με σπούδασαν και μου δώσανε όλα τα εφόδια για να γίνω σωστός άνθρωπος.

- Όλο το προσωπικό της Σχολής Εφαρμοσμένων Επιστημών του ΤΕΙ Κρήτης νυν Ελληνικό Μεσογειακό Πανεπιστήμιο που μου δώσανε με τις Σπουδές μου στο Προπτυχιακό Κύκλο Σπουδών τα εφόδια να τελειώσω το Τμήμα Ηλεκτρονικής.

- Τον εισηγητή μου Δρ. Αντώνη Κωνσταντάρα που μου έδωσε την ευκαιρία να εμπλουτίσω τις γνώσεις μου πάνω στο αντικείμενο της ΙοΤ Τεχνολογίας.

- Και στο τέλος τον μέντορα και συνεργάτη μου Γεώργιο Λιοδάκη για τις πολλές και πολύωρες συζητήσεις που κάναμε πάνω σε θέματα δικτύων Η/Υ και ΙοΤ.

# **Abstract:**

In this Thesis we are dealing with the Objective for another possibility to deliver the per scripted medication to the patient by using IoT Technology.

The terminology IoT Technology is in the present day a way to make things easier and better. It has penetrated in all possible dimensions and ways into everyday work and flows.

One of these innovations is an autonomous vehicle following a designated route using the following the Line Algorithm and Technology. This automation seems to be used also in other possible ways.

Our difference is that we use the same implementation supervised by a microcomputer Raspberry PI for the specific and special deliverance of Medication on an autonomous vehicle following a designated route. The implementation of this system consisted of a wireless network, devices and sensors which have been deployed in a way to fulfill the requirements. The program in this network is achieved by using Python as a programming language. The purpose of this network is supervising the autonomous vehicle, input of the different deliverance variables (which medication box port applies to which patient) designed from Scratch.

We call this Project MEDIBERRY. Automatic Medication Dispenser using Raspberry Pi.

# Σύνοψη:

Σε αυτή την εργασία θα ασχοληθούμε με στόχο την δυνατότητα παράδοσης φαρμάκων σε ασθενείς χρησιμοποιώντας την τεχνολογία ΙοΤ.

Η τεχνολογία ΙοΤ είναι σήμερα ένας τρόπος για να διευκολύνουμε και να βελτιώσουμε τα πράγματα. Έχει διεισδύσει σε όλες τις δυνατές πτυχές και διαστάσεις και τρόπους της καθημερινότητας στον εργασιακό και ιδιωτικό χώρο και όχι μόνο.

Μία από αυτές τις καινοτομίες είναι η χρήση ενός αυτόνομου οχήματος ακολουθώντας μια προκαθορισμένη διαδρομή χρησιμοποιώντας τον Αλγόριθμο παρακολούθησης γραμμής. Αυτή η αυτοματοποίηση φαίνεται να χρησιμοποιείται και με άλλους πιθανούς τρόπους και συνδυασμούς.

Η διαφορά μας είναι ότι χρησιμοποιούμε την ίδια εφαρμογή που ελέγχεται από έναν μικροϋπολογιστή Raspberry PI για την ειδική παράδοση φαρμάκων πάνω σε αυτόνομο όχημα ακολουθώντας μια προκαθορισμένη διαδρομή. Η εφαρμογή αυτού του συστήματος περιλαμβάνει ένα ασύρματο δίκτυο, διάφορες συσκευές και αισθητήρες που αλληλοεπιδρούν κατά τρόπο που να ικανοποιεί τις απαιτήσεις μας.

Ο προγραμματισμός σε αυτό το δίκτυο επιτυγχάνεται με τη χρήση της γλώσσας προγραμματισμού Python.

Ο σκοπός αυτού του δικτύου είναι η επίβλεψη του αυτόνομου οχήματος, η εισαγωγή των διαφορετικών μεταβλητών απελευθέρωσης (της αντίστοιχης θυρίδας φαρμάκων που ισχύει για τον ασθενή και που σχεδιάστηκε από το μηδέν).

Ονομάζουμε αυτό το Project MEDIBERRY προερχόμενο από τα αρχικά

Αυτόματος Διανομέας Φαρμάκων με χρήση Raspberry Pi.

# Περιεχόμενα

| Κεφάλαιο 1  | 0             |

|-------------|---------------|

| K SWAYAIO I | $\overline{}$ |

| 1 1 17 17   |               |

| 1.1 Περίληψη                                                     | 10 |

|------------------------------------------------------------------|----|

| 1.2 Κίνητρο για την Διεξαγωγή της Εργασίας                       | 11 |

| 1.3 Σκοπός και Στόχοι Εργασίας                                   | 12 |

| 1.4 Δομή Εργασίας                                                | 13 |

| <u>Κεφάλαιο 2°</u>                                               |    |

| 2.1 Τι είναι Τεχνολογίες του Internet (Internet of Things – IoT) | 15 |

| 2.2 Τεχνολογίες που χρησιμοποιούμε στο Internet of Things        | 15 |

| 2.3 Κίνδυνοι και προκλήσεις των Internet of Things               | 16 |

| 2.4 Οφέλη της χρήσης του Internet of Things (IoT)                | 17 |

| 2.5 Προκλήσεις του ΙοΤ                                           | 17 |

| 2.6 Πεδίο εφαρμογών του Internet of Things (IoT)                 | 17 |

| <u>Κεφάλαιο 3°</u>                                               |    |

| 3.1 Γνωριμία με το Raspberry Pi                                  | 19 |

| <u>Κεφάλαιο 4°</u>                                               |    |

| 4.1 Follow the Line με Raspberry Pi                              | 21 |

| 4.2 Λειτουργία και τεχνική ακολούθησης γραμμής (Line Follower)   | 21 |

| 4.3 Κυκλωματικό διάγραμμα για την ακολούθηση γραμμής             | 25 |

| 4.4 Προγραμματισμός για την ρουτίνα για την ακολούθηση γραμμής   | 28 |

| 4.5 Τροχοφόρο όχημα σε κίνηση με αλγόριθμο ανίχνευσης γραμμής    | 30 |

| 4.6 RFID                                                         | 36 |

| 4.7 Relays                                                       | 43 |

| 4.8 Μαννητικός αισθητήρας                                        | 45 |

| <b>4.9 Servo κινητήρες</b>                                                                                          |

|---------------------------------------------------------------------------------------------------------------------|

| <u>Κεφάλαιο 5°</u>                                                                                                  |

| <b>5.1Εισαγωγικά</b> 51                                                                                             |

| 5.2 Βήματα για την διασύνδεση της μονάδας Raspberry Pi με τον Υπολογιστή $51$                                       |

| <b>5.3</b> Βήματα για την αυτοματοποιημένη εκκίνηση της μονάδας Raspberry54                                         |

| $V_{\rm con}(\hat{a})$ and $6^{\circ}$                                                                              |

| <u>Κεφάλαιο 6°</u> <b>6.1 Εισαγωγικά</b>                                                                            |

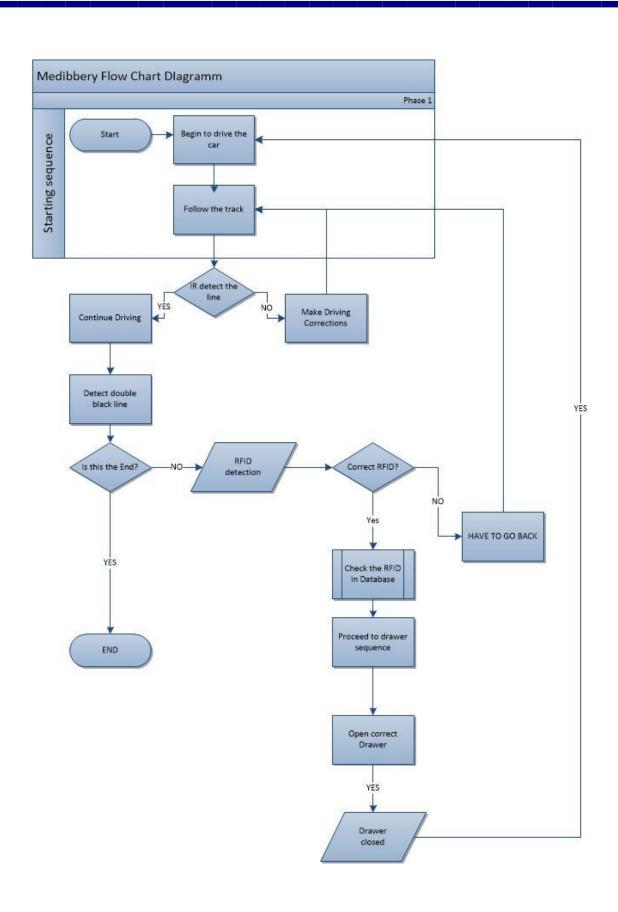

| 6.2 Διάγραμμα ροής της υλοποίησης                                                                                   |

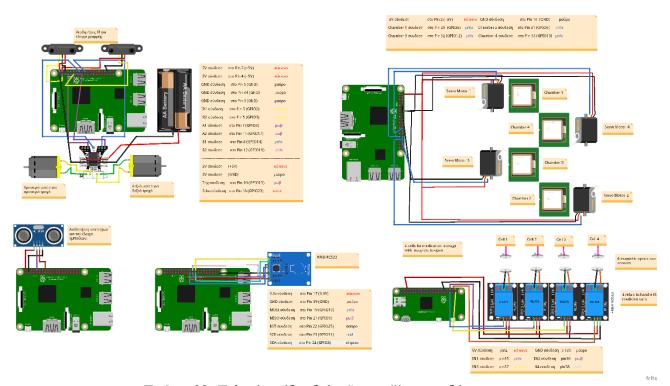

| <b>6.3 Το πλήρες σχέδιο σε Fritzing</b> 60                                                                          |

| <b>6.4 Το πλήρες πρόγραμμα σε Python</b> 61                                                                         |

| 6.5 Σενάρια Υλοποίησης                                                                                              |

| a. Υλοποίηση σε πλήρη λειτουργία67                                                                                  |

| <b>b.</b> Υλοποίηση με RFID σε λάθος θέσεις67                                                                       |

| c. Υλοποίηση με εμπόδιο στην διαδρομή67                                                                             |

|                                                                                                                     |

| <u>Κεφάλαιο 7°</u><br><b>Μελλοντικές επεκτάσεις</b> 69                                                              |

| <b>Μειονεκτήματα</b> 69                                                                                             |

| Πλεονεκτήματα69                                                                                                     |

|                                                                                                                     |

| <u>Κεφάλαιο 8°</u><br>Συμπεράσματα70                                                                                |

| <u>Κεφάλαιο 9°</u>                                                                                                  |

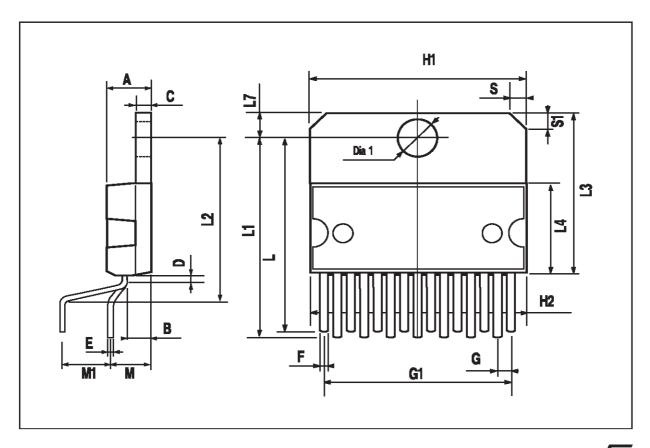

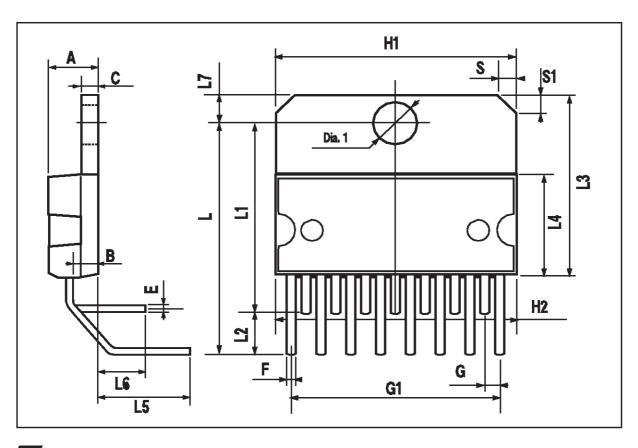

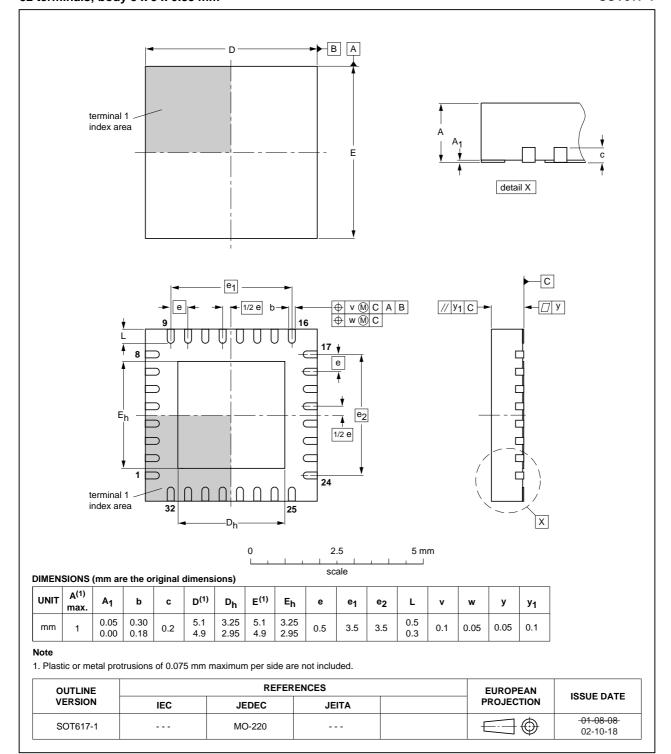

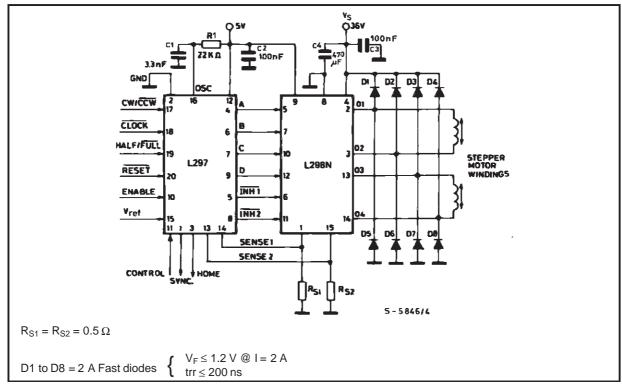

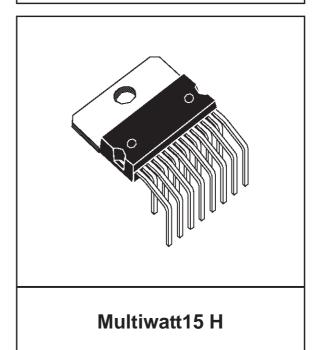

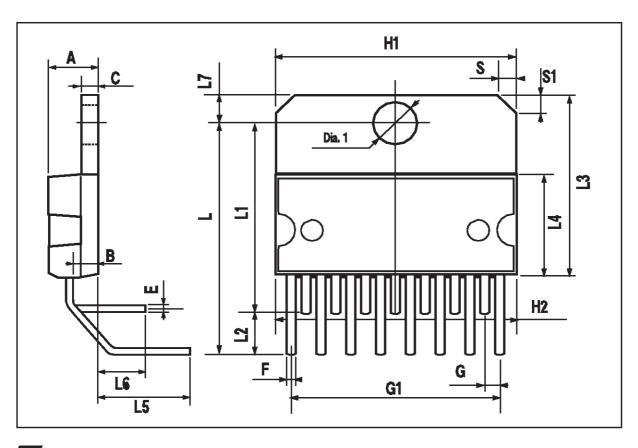

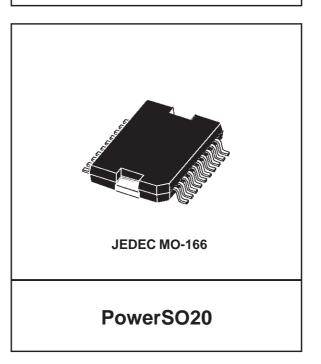

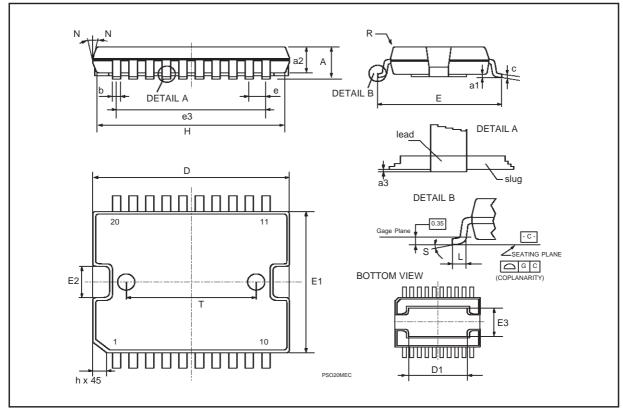

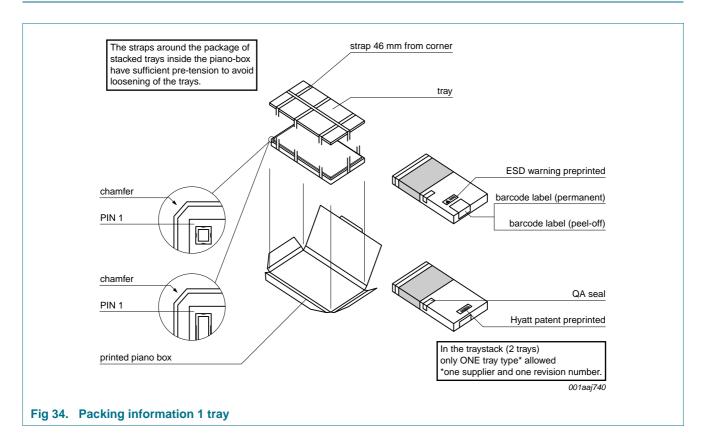

| 9.1 Βιβλιογραφία       71         9.2 Data Sheets       Appendix 1-156         • L298 Driver Motor       Appendix 2 |

| • | L298N-module-Information      | Appendix 16 |

|---|-------------------------------|-------------|

| • | IR Sensor                     |             |

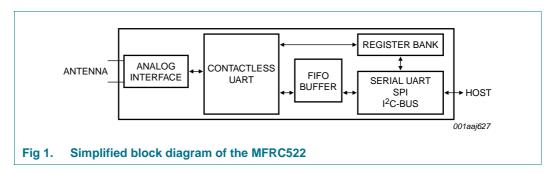

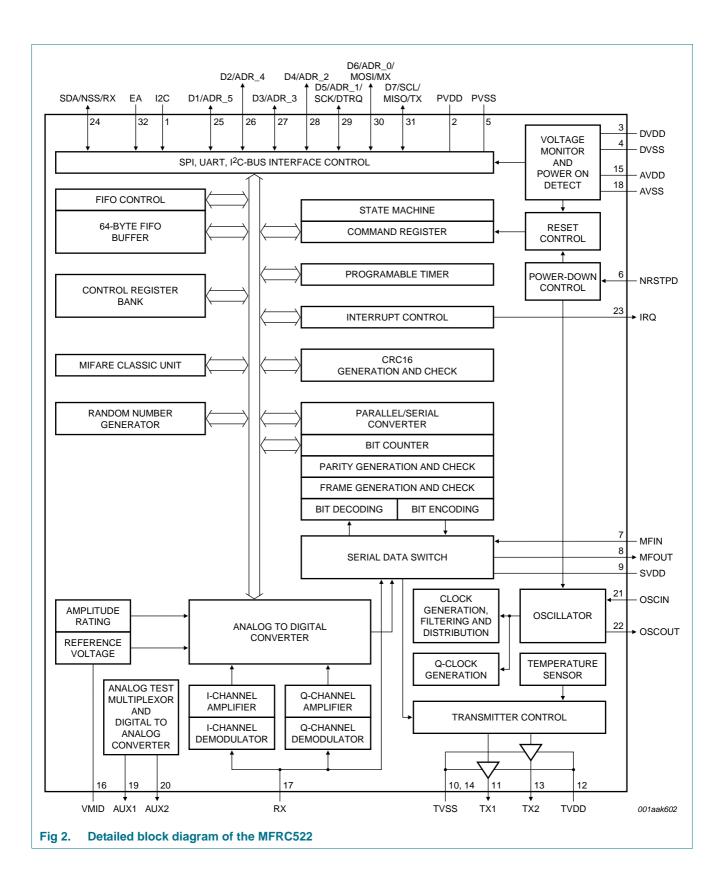

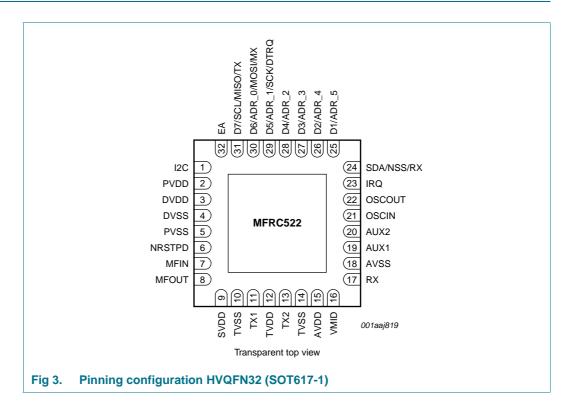

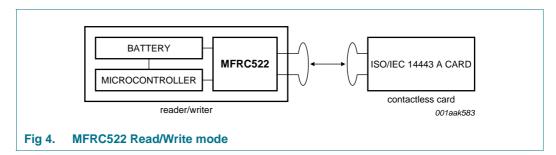

| • | MFRC522 Contactless Reader IC | Appendix 26 |

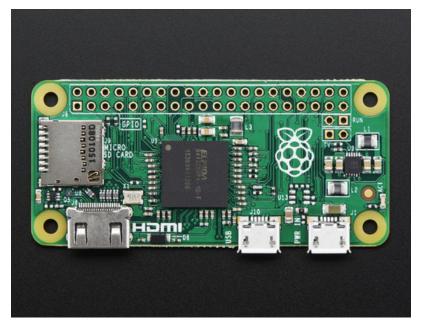

| • | Raspberry PI                  |             |

|   | Server Motor SG90             |             |

# Λίστα Σχημάτων

| Σχήμα 1: Το '20 θα έχουμε τουλάχιστον 50 δις ΙοΤ συσκευές                            |

|--------------------------------------------------------------------------------------|

| Σχήμα 2α: Διασύνδεση των πάντων                                                      |

| Σχήμα 2β: Τρόποι και λόγοι διασύνδεσης                                               |

| Σχήμα 3: Πεδία εφαρμογών του Internet of Things                                      |

| <b>Σχήμα 4</b> : Smart Document management σε γραφεία18                              |

| Σχήμα 5: Πεδία εφαρμογών ΙοΤ τεχνολογίας                                             |

| <b>Σχήμα 6</b> : Διάφορα μοντέλα Raspberry Pi και οι δυνατότητες τους19              |

| Σχήμα 7: Raspberry Pi 3 model B                                                      |

| <b>Σχήμα 8</b> : Raspberry Pi δίτροχο αμαξίδιο με αισθητήρια για ανίχνευση γραμμής21 |

| Σχήμα 9: α) με άσπρη ανακλώμενη επιφάνεια β) σε μαύρη ανακλώμενη επιφάνεια22         |

| <b>Σχήμα 10</b> : ΙR αισθητήρες HW-006 για την υλοποίηση22                           |

| Σχήμα 11: Μπλοκ διάγραμμα οδήγησης των τροχών από τους ΙR αισθητήρες25               |

| Σχήμα 12: Follow the Line with Fritzing                                              |

| <b>Σχήμα 13</b> : Διάταξη του GPIO Header στις διάφορες εκδόσεις Raspberry Pi26      |

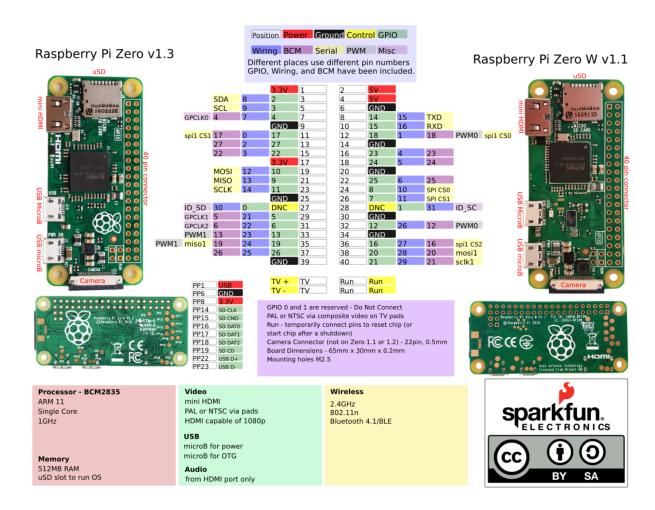

| <b>Σχήμα 14</b> : Raspberry Pi Zero v1.3 vs v1.1                                     |

| Σχήμα 15: Έτοιμο όχημα για την υλοποίηση Follow the Line                             |

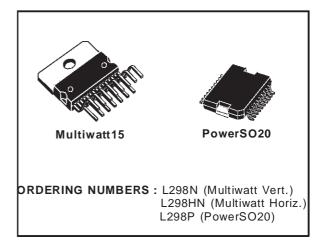

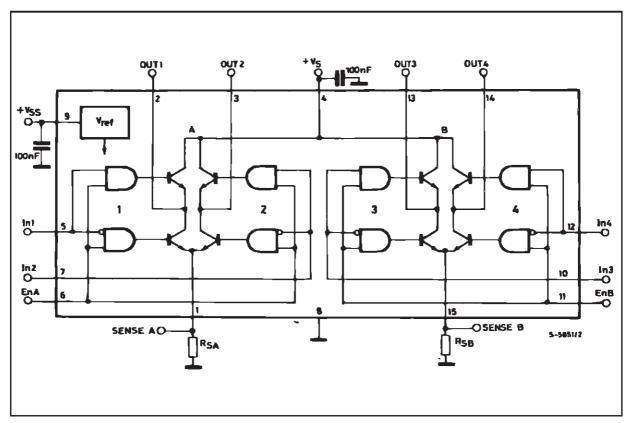

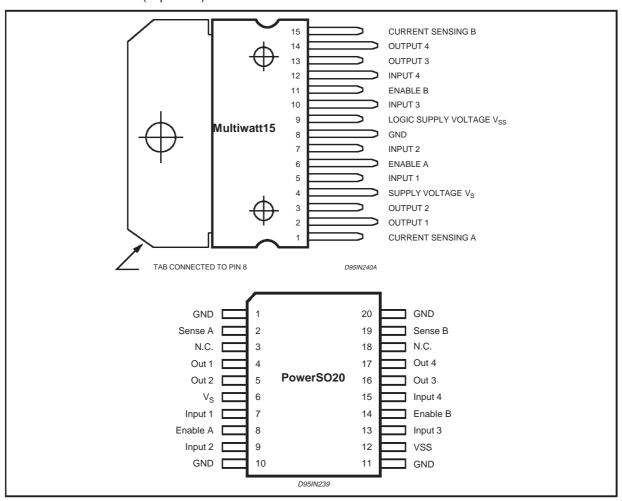

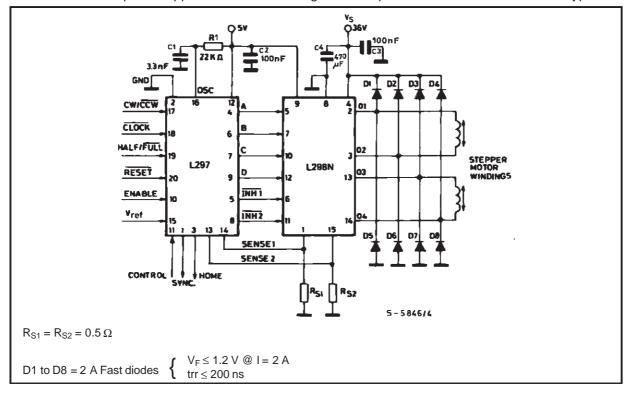

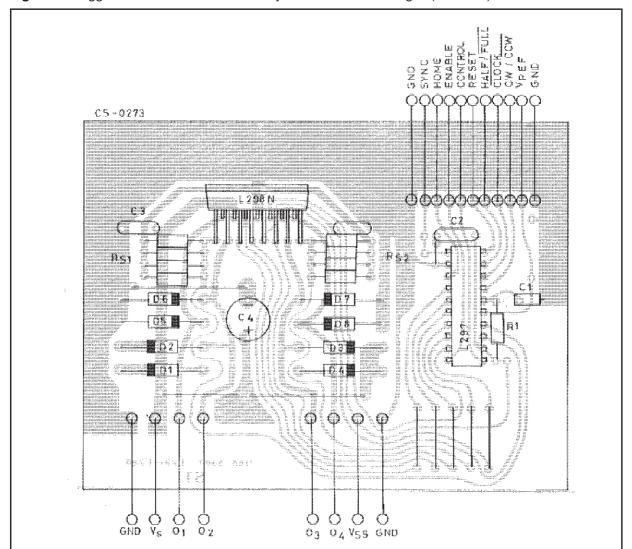

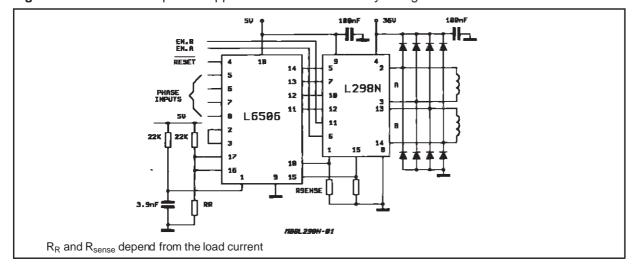

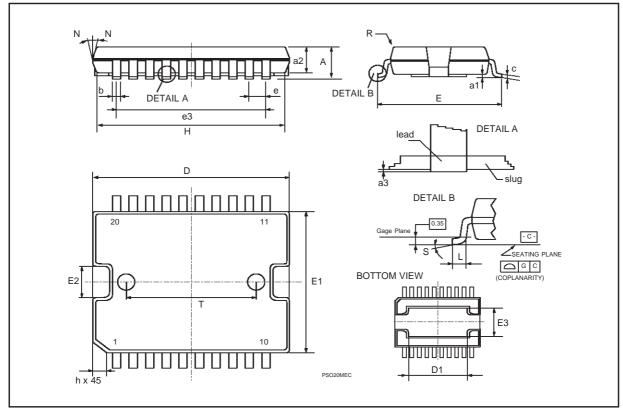

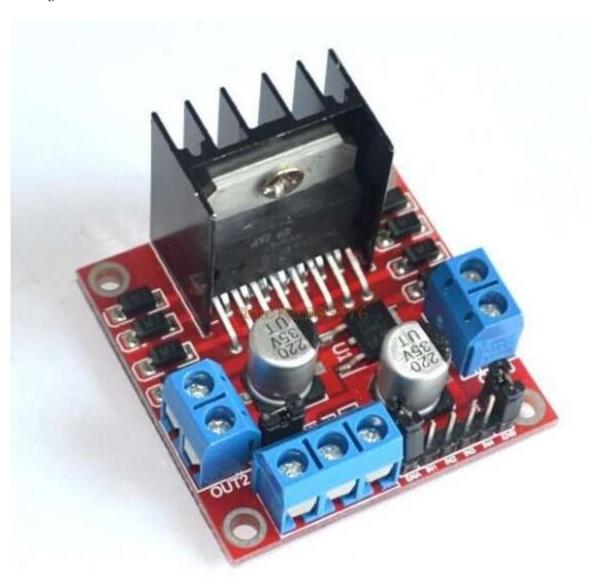

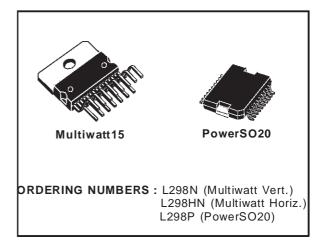

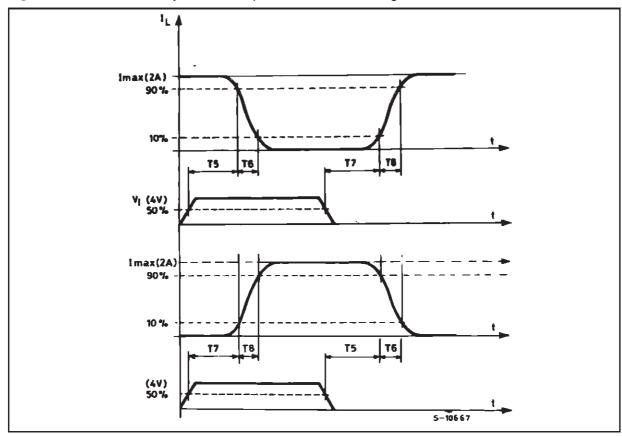

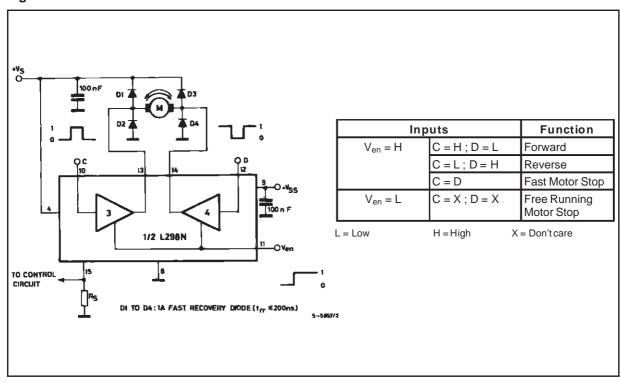

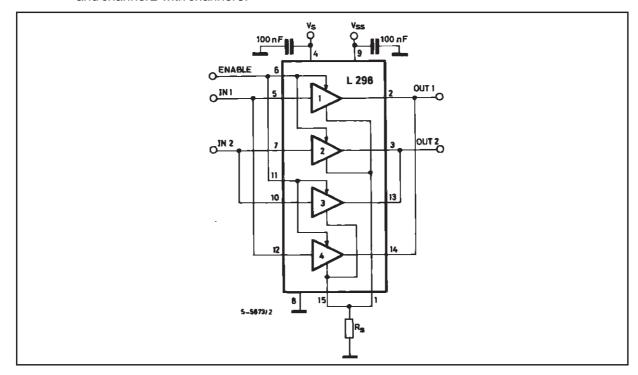

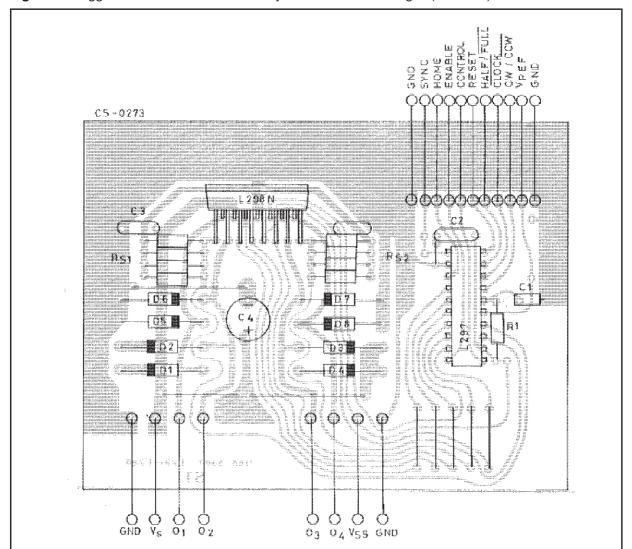

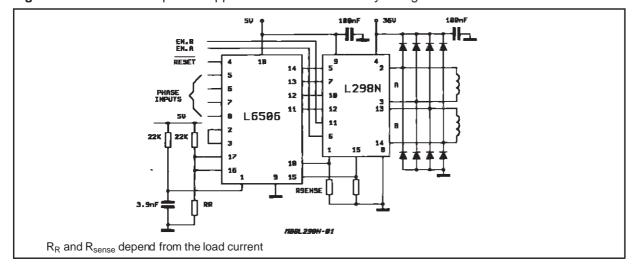

| <b>Σχήμα 16</b> : L298 Motor Driver                                                  |

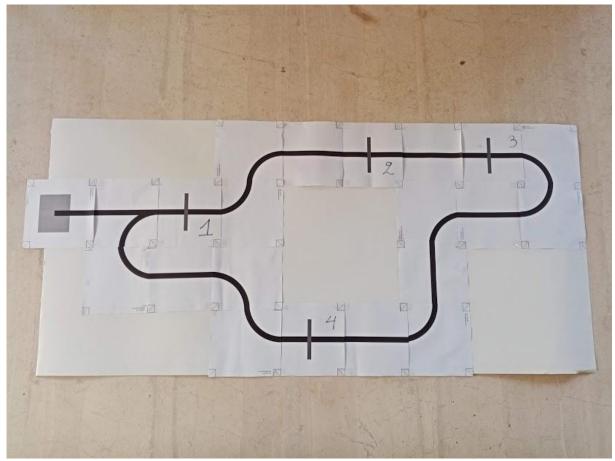

| Σχήμα 17: Εικονική δοκιμαστική διαδρομή                                              |

| Σχήμα 18: Πραγματική δοκιμαστική διαδρομή                                            |

| <b>Σχήμα 19</b> : Αισθητήρας υπερήχων HC-SR0434                                      |

| Σγήμα 20: Αργή λειτουργίας Ultrasonic Sensor                                         |

| Σχήμα 21: Σύνδεση του αισθητήρα υπερήχων HC-SR04 στο Ra                                      | spberry35               |

|----------------------------------------------------------------------------------------------|-------------------------|

| Σχήμα 22: RFID tags τύπου κάρτας και ετικέτας                                                | 37                      |

| Σχήμα 23: Pin layout στο RFID-RC522                                                          | 39                      |

| <b>Σχήμα 24</b> : Διασύνδεση του Raspberry Pi με το RFID-RC522                               | 39                      |

| <b>Σχήμα 25</b> : Relays 4 καναλιών                                                          | 44                      |

| Σχήμα 26: Αποτύπωση σε Fritzing για τη χρήση 4 Relays                                        | 45                      |

| <b>Σχήμα 27</b> : Μαγνητικός αισθητήρας ΟΝ/ΟFF                                               | 46                      |

| Σχήμα 28: Παραστατικός τρόπος λειτουργίας του μαγνητικού αι                                  | σθητήρα47               |

| Σχήμα 29: Micro Step motor τύπου Tower Pro και διάταξη ακρο                                  | δεκτών47                |

| Σχήμα 30: Αποτύπωση σε Fritzing για τη χρήση 4 Micro Server                                  | Motor48                 |

| Σχήμα 31: <b>A</b> ) Pill box ευρείας χρήσης <b>B</b> ) Κάτοψη Pill box Γ) Πλαΐνη όψη με εγκ | οπές χωρίς αισθητήρια49 |

| Σχήμα 32: Pill box με αισθητήρες μαγνητικούς και micro servo ι                               | ςινητήρα50              |

| Σχήμα 33: Ρυθμίσεις για πρόσβαση ssh                                                         | 53                      |

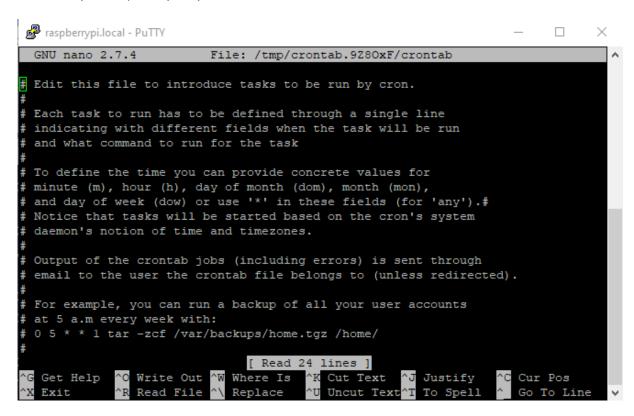

| Σχήμα 34: Αρχική οθόνη στο Crontab                                                           | 55                      |

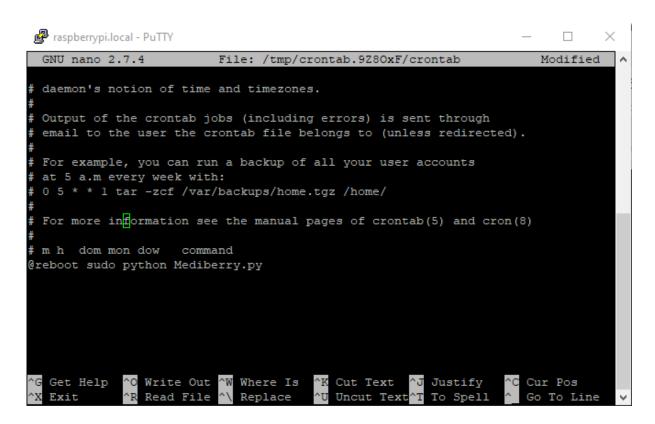

| Σχήμα 35: Οθόνη στο Crontab μετά την εισαγωγή του script μας                                 | 56                      |

| Σχήμα 36: Αρχική οθόνη εκτέλεσης                                                             | 57                      |

| Σχήμα 37: Πλήρες διάγραμμα ροής "Mediberry"                                                  | 59                      |

| Σγήμα 38: Τελικό σγέδιο διάταξης μαζί με συνδέσεις                                           | 60                      |

# Κεφάλαιο 1°

#### 1.1 Περίληψη

Σήμερα, το Internet of Things πιάνει ένα όλο και μεγαλύτερο κομμάτι στην αγορά των τεχνολογιών καθώς προσφέρει λύσεις και ευκολία στην καθημερινότητα ενός ανθρώπου. Ένα απλό δίκτυο αισθητήρων μπορεί να προσφέρει λύσεις από την πιο απλούστερη π.χ. αισθητήρια για την παρακολούθηση της θερμοκρασίας σε δωμάτιο μέχρι και την πιο σύνθετη αυτής, της απομακρυσμένης παρακολούθησης μιας μονάδας π.χ. ενός ρομπότ σε άλλο πλανήτη. Επιπλέον, με τα Smartphones να αποτελούν πλέον αναπόσπαστο κομμάτι της ζωής μας η διαχείριση και η παρακολούθηση τέτοιων συστημάτων έχει γίνει πιο εύκολη και προσιτή από ποτέ και συν τοις άλλης μας επιτρέπει την παραμετροποίηση και παρέμβαση οποιαδήποτε στιγμή και αν χρειαστεί.

Οι οικιακοί αυτοματισμοί είναι ένα άλλο πεδίο εφαρμογής του Internet of Things που ανήκει στην κατηγορία των εφαρμογών για καταναλωτές και είναι συνεχώς σε εξέλιξη με νέες πλατφόρμες, τεχνολογίες και Hardware να βγαίνουν κάθε τόσο. Ένας οικιακός αυτοματισμός μπορεί να προσφέρει οικονομία καθώς κάνει την παρακολούθηση σε κατανάλωση ενέργειας πιο εύκολη από ποτέ, προσφέρει ασφάλεια με την εγκατάσταση ενός δικτύου αισθητήρων και κάμερες και την ακόμη ευκολότερη εξ' αποστάσεως διαχείριση όλων των διασυνδεδεμένων έξυπνων οικιακών συσκευών.

Η υλοποίηση προσφέρει επίσης ευφυής αυτοματισμούς καθώς στην αλλαγή της κατάστασης κάποιων αντικειμένων ενεργοποιούνται άλλοι μηχανισμοί του συστήματος μέσω της υλοποίησης κάποιων κανόνων που θα εξηγήσουμε σε παρακάτω ενότητα. Το σύστημα αυτό με τις κατάλληλες τροποποιήσεις και χρήση αισθητήρων μπορεί να χρησιμοποιηθεί και για άλλες εφαρμογές αυτοματισμού στο πλαίσιο υλοποιήσεων των Internet of Things όπως για παράδειγμα, εφαρμογές τηλεϊατρικής, εκπαίδευσης ή διανομής εμπορευμάτων.

#### 1.2 Κίνητρο για την Διεξαγωγή της Εργασίας

Τα τελευταία χρόνια, λόγω της ραγδαίας ανάπτυξης των συσκευών που συνδέονται στο διαδίκτυο και ελέγχονται μέσω αυτού, έχει οδηγήσει το Internet of Things να είναι αρκετά δημοφιλές και να αναπτύσσονται διάφορες εφαρμογές στο πεδίο αυτό. Όλο και περισσότερες επιχειρήσεις έχουν αρχίσει να υιοθετούν εφαρμογές που να πουλούν τεχνολογικά προϊόντα σχετικά με το Internet of Things για την χρήση στους καταναλωτές.

Παρ' όλα αυτά αν κάποιος χρήστης θέλει να στήσει ένα ολοκληρωμένο σύστημα αυτοματισμού από τα προϊόντα αυτά θα χρειαστεί να παραμετροποίηση τις συσκευές ώστε να πληρούν τα διαφορετικά ζητούμενα των εφαρμογών.

Για αυτό τον λόγο σε αυτή την εργασία αναπτύσσεται ένα σύστημα αυτοματισμού που να υλοποιεί την αρχική ιδέα της στοχευμένης παράδοσης φαρμάκων σε πελάτες σε έναν Smart κόσμο με την χρήση ενός δικτύου μικροελεγκτών και αισθητήρων και τις εξ' αποστάσεως διαχείρισης και ελέγχου. Ένα άλλο ζητούμενο είναι πως μπορούμε να κρατήσουμε το κόστος χαμηλό και τι ευελιξία μας προσφέρει αυτό το σύστημα, ώστε να μπορεί ανά πάσα στιγμή να παραμετροποιηθεί και για άλλα πεδία εφαρμογών και χώρων.

#### 1.3 Σκοπός και Στόχοι Εργασίας

Σκοπός της εργασίας είναι η δημιουργία ενός ευέλικτου συστήματος με χαμηλό κόστος για την απομακρυσμένη παράδοση χαπιών σε πελάτες με τη χρήση ενός αυτόνομου τροχοφόρου οχήματος μέσα σε έναν κλειστό και προδιαγραμμένο χώρο. Στόχος είναι η ανάπτυξη και εφαρμογή ενός λογισμικού για την εισαγωγή αρχικών παραμέτρων και δεδομένων, της διαδρομής, τους τελικούς αποδέκτες, σε πλατφόρμα ικανή να τρέξει σε οποιοδήποτε Smartphone ή και έναν ηλεκτρονικό υπολογιστή καθώς και την ανάπτυξη και υλοποίηση εφ' όσον το δίκτυο των συσκευών μας είναι συνδεδεμένο με το διαδίκτυο να παρακολουθεί την κατάσταση του οχήματος, αλλά και να αλληλοεπιδρά με τις συσκευές οποιαδήποτε στιγμή αυτό χρειαστεί.

Σε αυτή την εργασία θα ασχοληθούμε με στόχο την δυνατότητα στοχευμένης παράδοσης φαρμάκων σε ασθενείς χρησιμοποιώντας τη τεχνολογία IoT.

Η τεχνολογία ΙοΤ είναι σήμερα ένας τρόπος για να διευκολύνουμε και να βελτιώσουμε τα πράγματα. Έχει διεισδύσει σε όλες τις δυνατές διαστάσεις και τρόπους της καθημερινότητας στον εργασιακό χώρο και όχι μόνο.

Μία από αυτές τις καινοτομίες είναι και η χρήση ενός αυτόνομου οχήματος ακολουθώντας μια προκαθορισμένη διαδρομή χρησιμοποιώντας έναν Αλγόριθμο του τύπου παρακολούθησης γραμμής. Αυτή η αυτοματοποίηση φαίνεται να χρησιμοποιείται και με άλλους πιθανούς τρόπους και συνδυασμούς.

Η ουσιαστική διαφορά μας είναι ότι θα χρησιμοποιούμε ως καρδιά του συστήματος έναν μικροϋπολογιστή τύπου Raspberry Pi. Η ειδική παράδοση των φαρμάκων πάνω σε ένα αυτόνομο τροχοφόρο όχημα ακολουθώντας μια προκαθορισμένη διαδρομή. Η εφαρμογή αυτού του συστήματος περιλαμβάνει ένα ασύρματο δίκτυο, διάφορες συσκευές και αισθητήρες που αλληλοεπιδρούν κατά τρόπο που να ικανοποιεί τις απαιτήσεις μας.

Όλα αυτά θα δρουν αυτόνομα (σχεδιάστηκε από το μηδέν) και η επικοινωνία σε αυτό το δίκτυο επιτυγχάνεται με τη χρήση της γλώσσας προγραμματισμού Python.

Ο σκοπός αυτού του δικτύου είναι η επίβλεψη του αυτόνομου οχήματος, η εισαγωγή των διαφορετικών μεταβλητών απελευθέρωσης (της αντίστοιχης θυρίδας φαρμάκων που ισχύει για τον ασθενή) σε αλληλεπίδραση με τον αποδέκτη εάν αυτός είναι παρόν ή όχι. Η συνέχιση στον επόμενο σταθμό παράδοσης και την επιτυχή ολοκλήρωση της διαδρομής και επαναφορά στην βάση του.

Ονομάζουμε αυτό το Project MEDIBERRY προερχόμενο από τα αρχικά Αυτόματος Διανομέας Φαρμάκων με χρήση Raspberry Pi.

#### 1.4 Δομή Εργασίας

Στην παρούσα εργασία στο κεφάλαια **2°** γίνετε αναφορά στις τεχνολογίες του Internet of Things και των ασυρμάτων δικτύων αισθητήρων, οι οποίες αποτελούν την βάση για την υλοποίηση ενός σύγχρονου αυτοματισμού.

Στο κεφάλαιο  $3^{\circ}$  περιγράφεται ο μικροεπεξεργαστής Raspberry Pi και τι δυνατότητες έχει με το εξωτερικό περιβάλλον και θα γίνει και μια εισαγωγή στον τρόπο χρήσης και παραμετροποίησης για το δικό μας σκοπό.

Στο κεφάλαιο **4°** περιγράφονται αναλυτικά τα προ απαιτούμενα στάδια υλοποίησης για κάθε σημείο αναφοράς και παράδοσης και παρουσίαση σεναρίων λειτουργίας του συστήματος με εικόνες.

Στο κεφάλαιο **5°** πως θα χρησιμοποιηθεί λεπτομερώς βήμα προς βήμα το λογισμικό Python για την διασύνδεση Raspberry Pi με το σύστημα του Η/Υ ή και φορητού.

Εν συνεχεία, στο κεφάλαιο **6°** ακολουθώντας όλα τα στάδια που προαναφέρθηκαν θα παρουσιαστεί στο σύνολο της η υλοποίηση για την δικιά μας περίπτωση και θα αναφερθούμε σε βασικά σενάρια κατάστασης του αυτοματισμού σε πραγματικό περιβάλλον βάζοντας τις αντίστοιχες παραμέτρους.

Στο **7**<sup>0</sup> κεφάλαιο περιγράφονται μελλοντικές επεκτάσεις του συστήματος, αναφορά σε μειονεκτήματα και συνολική αξιολόγηση της εργασίας που θα μπορούσε να έχει η παρούσα εφαρμογή.

Τέλος στο 8° κεφάλαιο θα έχουμε αναφορά στα Συμπεράσματα.

Η παρούσα διατριβή ολοκληρώνετε με το  $9^{\circ}$  κεφάλαιο το οποίο περιλαμβάνει την **Βιβλιογραφία**, **Πηγές** και **Τεχνικά Φυλλάδια** των χρησιμοποιημένων συσκευών και αισθητηρίων καθώς και τον αναλυτικό κώδικα της εφαρμογής.

## Κεφάλαιο 20

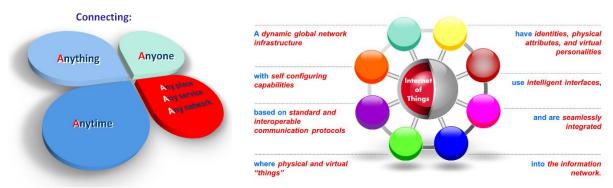

#### 2.1. Τι είναι Τεχνολογίες του Internet (Internet of Things – IoT)

Το Internet of Things ή διαδίκτυο των πραγμάτων είναι μια νέα εφαρμογή τεχνολογιών που ανθίζει από τα τέλη της δεκαετίας του '90 και πιο συγκεκριμένα το 1999. Ο Kevin Ashton¹ αποτελεί μέλος της ομάδας που ανακάλυψε τον τρόπο σύνδεσης των συσκευών με το διαδίκτυο, κατά την παρουσίαση του επιτεύγματος αυτού αναφέρθηκε για πρώτη φορά ο όρος the Internet of Things και από τότε και ύστερα καθιερώθηκε η χρήση τους.

Περιγράφετε με απλά λόγια ως οι συσκευές και περιφερειακά που χρησιμοποιούν ενσωματωμένους αισθητήρες για τη συλλογή και μετάδοση δεδομένων ή την ανάληψη κάποιας δράσης βάσει αυτών.

Οι συσκευές αυτές είναι συνδεδεμένες σε τοπικό δίκτυο ή και το Internet και συλλέγουν, ανταλλάσσουν πληροφορίες και επικοινωνούν μεταξύ τους με απλές διακριτές μεθόδους και κατά τρόπο τέτοιο, ώστε να υλοποιούν τα προ απαιτούμενα.

Η ιδέα πίσω από αυτό είναι η διασύνδεση όλων των ηλεκτρονικών συσκευών (αισθητήρων και μη) μεταζύ τους ή και ακόμα η διασύνδεση τους με το Internet.

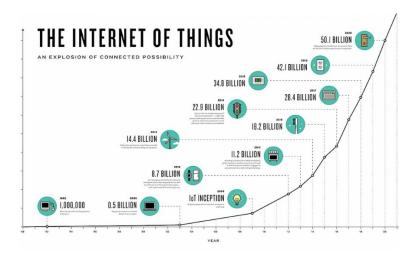

Η Cisco σε μια έρευνα που έκανε και βάση της διαφαινόμενης ανάπτυξης προέβλεψε ότι αρχές της επόμενης δεκαετίας (δεκαετία του '20) θα έχουμε κατ' εκτίμηση περίπου 50 δισεκατομμύρια συσκευές διασυνδεδεμένες με το Internet.

Σχήμα 1: Το '20 θα έχουμε τουλάχιστον 50 δις ΙοΤ συσκευές<sup>2</sup>

Και αυτές θα αυξηθούν ακόμη περισσότερο όσο θα υλοποιούμε όλο και περισσότερες εφαρμογές στο Internet. Εμάς σκοπός μας δεν είναι να κρίνουμε ή να ερευνήσουμε αν το ίδιο το Internet στην παρούσα φάση έχει την δυνατότητα να ανταπεξέλθει στο πλήθος των διαφαινόμενων εφαρμογών ούτε μας ενδιαφέρει αν θα μεταβεί ταχέως σε 5G ή και ακόμα 6G.

\_

Wikipedia αναφορά στον Kevin Ashton ερευνητή και πρωτοστάτη της Τεχνολογίας ΙοΤ.

<sup>&</sup>lt;sup>2</sup> What is the Internet of Things,

Σχήμα 2α: Διασύνδεση των πάντων

Σχήμα 2β: Τρόποι και λόγοι διασύνδεσης

## 2.2. Τεχνολογίες που χρησιμοποιούμε στο Internet of Things

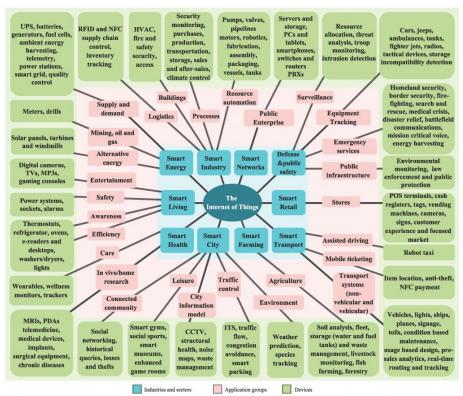

Οι τεχνολογίες που χρησιμοποιούμε αφορούν σε ποια πεδία θα θέλαμε να εφαρμόσουμε αυτή τη νέα τεχνολογία. Σε γενικές γραμμές βγαίνει το slogan ...

# Μπορούμε να συνδέσουμε τα πάντα με τα πάντα!!!

Σχήμα 3: Πεδία εφαρμογών του Internet of Things

### 2.2 Οφέλη της χρήσης του Internet of Things (IoT)

Καμία τεχνολογική εφαρμογή δεν παράγει περισσότερα **DATA** από το **Internet of Things** και όταν πρόκειται για **BIG DATA** μιλάμε για τεράστιους όγκους δεδομένων.

Ακούμε συνεχώς για το Internet of Things αλλά που είναι;

Πότε θα γίνει μέρος της καθημερινότητάς μας;

Που είναι οι αμέτρητες συσκευές-αισθητήρες που θα συνδέονται στο Internet;

Υπάρχει ζήτηση στην αγορά;

Έχει ωριμάσει η τεχνολογία;

Πρέπει να ξεκαθαρίσουμε την κατάσταση παρουσιάζοντας μερικά χαρακτηριστικά παραδείγματα από βιομηχανίες που ενσωματώνουν τεχνολογίες ΙοΤ όχι στο μέλλον, αλλά στο παρόν.

# Ο χώρος του ΙοΤ χωρίζετε σε δύο βασικές κατηγορίες.

**Στην πρώτη** έχουμε την καταναλωτική αγορά και τις διάφορες συνδεδεμένες συσκευές και **στη δεύτερη** τις συσκευές βιομηχανικού αυτοματισμού διασυνδεμένες μεταξύ τους.

Ωστόσο, ο χρήστης χρειάζεται τρανταχτά παραδείγματα βγαλμένα μέσα από τη ζωή του για να αντιληφθεί το πραγματικό όφελος του ΙοΤ.

Ενα από αυτά είναι η αυτοκινητοβιομηχανία η οποία από την πρώτη στιγμή υιοθέτησε τη συγκεκριμένη τεχνολογία. Μπορεί στην Ελλάδα να μην την έχουμε στην πράξη ακόμα, αλλά σε ΗΠΑ και Δ. Ευρώπη τα περισσότερα οχήματα πωλούνται με ενσωματωμένη συνδεσιμότητα και (συνδρομητικές) υπηρεσίες υποστήριξης προς τον οδηγό (τεράστιο το όφελος στον επαγγελματικό κλάδο). Έτσι, όχι μόνο μπορεί να γίνει πρόβλεψη βλαβών και αντικατάσταση εξαρτημάτων (της μπαταρίας για παράδειγμα ή του προγραμματισμού για service στο πλησιέστερο συνεργείο) αλλά και η εταιρεία υποστήριξης μπορεί να ειδοποιήσει τον οδηγό ότι το αυτοκίνητό του είναι ξεκλείδωτο και να του το κλειδώσει εξ' αποστάσεως<sup>3</sup>. Δεν μιλάμε ότι οι λύσεις σε περιβάλλον cloud προκαλούν τις εταιρίες λογισμικού στο να αξιοποιήσουν και να ενσωματώσουν όλο και περισσότερες ιδέες και εφαρμογές στα διασυνδεδεμένα οχήματα. Αλλά τους βάζουν συνεχώς να εξελίσσουν όλο και περισσότερες γραμμές κώδικα και να αναπτύξουν μικροελεκτές και αισθητήρια για την κάλυψη των αναγκών. Και τι θα δούμε ακόμα στο μέλλον!

#### 2.3 Κίνδυνοι και προκλήσεις των ΙοΤ

Οι κίνδυνοι και προκλήσεις του ΙοΤ αφορούν στο πόσο μπορούμε τεχνολογικά να συνδέσουμε τα πάντα με τα πάντα. Υπάρχουν κάποια πεδία στην ιατρική π.χ. που δεν μπορούν ακόμα να αξιοποιήσουν στην πράξη την τεχνολογία αυτή. Είτε γιατί δεν έχει ακόμα ωριμάσει η τεχνολογία υλοποίησης τους είτε δεν είναι ακόμα εφικτό να παραμετροποιηθούν πλήρως τα δεδομένα ώστε να προχωρήσουμε στην υλοποίηση τους και να έχουμε όφελος τελικά. Οι κίνδυνοι από την άλλη είναι κυρίως η ασφάλεια των ΙοΤ που είναι πολύ πιο πολύπλοκη από την ασφάλεια συνηθισμένων και τυπικών τερματικών συσκευών. Στο ΙοΤ έχουμε μια πλειάδα έξυπνων συσκευών, όπως αισθητήρες, διασυνδεδεμένες πλακέτες, υποπλακέτες, συσκευές γενικότερα που συνδέονται σε κάποιο τοπικό δίκτυο και από εκεί στο Internet ή και κατ' ευθείαν στο Internet. Μπορεί επίσης να υλοποιούν και κάποια διαδικτυακή εφαρμογή την οποία έχουμε σχεδιάσει από το μηδέν ή την παρέχει ο κατασκευαστής με ή όχι πρόσβαση σε υπηρεσίες cloud. Σε όλη την διαδρομή και ακόμη περισσότερα τα ίδια τα ΙοΤ έχουν ευπάθειες και τρωτά σημεία. Η ασφάλεια του αισθητηρίου ή της συσκευής δεν αποτελεί προτεραιότητα στο μυαλό κάθε σχεδιαστή εφαρμογής. Απλά υλοποιούνε τις σχεδιαστικές ανάγκες αγνοώντας το θέμα ασφάλειας. Παράδειγμα θα μπορούσε να είναι ότι "εύκολα" μπορούμε να

\_

³ Τα πραγματικά οφέλη του IoT, Biztech.gr

παραβιάσουμε κάποιες Webcam αφού με μια καλή αναζήτηση στο Internet μπορούμε να βρούμε τα συνθηματικά για την διαχειριστική πρόσβαση πάνω τους και έτσι να εκμεταλλευτούμε και να αποσπάσουμε τα δεδομένα τους. Το λογισμικό που τρέχουν πολλές φορές δεν ενημερώνετε ή δεν αξιοποιεί όπως θα έπρεπε κάποια επίπεδα ασφαλείας και έτσι παραμένει εκτεθειμένο και απροστάτευτο σε εξωτερικές κακόβουλες επιθέσεις. Από την άλλη και οι ίδιες εφαρμογές που ελέγχουν αυτές δεν ενημερώνονται ή ο κατασκευαστής/σχεδιαστής δεν ενδιαφέρετε να τις ενημερώσεις δίνοντας έτσι άλλο ένα σημείο τροφής σε επιθέσεις. Δεν αποτελεί κάποιο φανταστικό σενάριο άλλα δυστυχώς είναι η καθημερινότητα και το σύνηθες σε αυτές τις περιπτώσεις.

#### 2.4 Οφέλη της χρήσης του Internet of Things (IoT)

Το ΙοΤ γενικότερα έχει τεράστια οφέλη. Δεν θα αναλύσουμε εδώ την ποικιλία των οφελών που έχει να προσφέρει αυτή η τεχνολογία για κάθε πτυχή της καθημερινότητας. Ας αναφερθεί ενδεικτικά σαν παράδειγμα η χρήση έξυπνων ετικετών σε φάρμακα. Έτσι μπορεί οποιοσδήποτε να παρακολουθήσει και να ελέγξει την διαδρομή από την παρασκευή μέχρι την κατανάλωση του φαρμάκου, κάτι το οποίο μέχρι σήμερα ήταν αδιανόητο χωρίς την νέα αυτή τεχνολογία. Πολλά είναι επίσης τα οικονομικά οφέλη που μπορούμε να έχουμε από την ορθή χρήση των ΙοΤ αισθητήρων και συσκευών.

Για παράδειγμα η εγκατάσταση ενός πλήρες ευφυούς σπιτιού μας επιτρέπει αν έχουμε σωστά παραμετροποίηση τα δεδομένα και τις αρχικές συνθήκες το σύστημα από μόνο του μόνο με επικοινωνία machine 2 machine (M2M) να ελέγχει το σπίτι ανοιγοκλείνοντας περιττά φώτα, ενεργοποίηση/απενεργοποίηση συναγερμού, ενεργοποίηση/απενεργοποίηση των κλιματιστικών, συμβάλλοντάς ουσιαστικά στην ορθότερη ενεργειακή διαχείριση και εξοικονόμηση χρημάτων και ορθότερη χρήση πόρων.

#### 2.5 Προκλήσεις του ΙοΤ

Αναμφίβολα η νέα τάση στον τομέα της τεχνολογίας είναι η αξιοποίηση της τεχνολογίας των ΙοΤ. Όλο και περισσότερες συσκευές και αισθητήρες διασυνδέονται είτε τοπικά είτε με τη χρήση του ΙΡ πρωτοκόλλου στο Internet. Αυτό εγείρει νέες προκλήσεις και κινδύνους που σπαζοκεφαλιάζουν οι τεχνικοί λογισμικού και δικτυακής ασφάλειας να προσπαθήσουν να ανιχνεύουν και να αποτρέψουν τρωτότητες ή εισόδους σε κακόβουλο λογισμικό. Οι πολλές φορές απλή φύση ή η σχεδίαση των αισθητήρων. Η πρόχειρη σχεδίαση και υλοποίηση στην ανάπτυξη του κώδικα, η πίεση χρόνου για την υλοποίηση της εφαρμογής, βοηθούν τους επίδοξους χάκερς να εισβάλλουν και να αντλούν ευαίσθητα δεδομένα ή να παίρνουν πλήρως τον έλεγχο των συσκευών αυτών. Άλλη πρόκληση είναι να σχεδιαστούν και να γίνουν άτρωτα τα συστήματα αυτά ως προς τις κυβερνοεπιθέσεις.

#### 2.6 Πεδίο εφαρμογών του Internet of Things (IoT)

Τα πεδία εφαρμογών των ΙοΤ δεν είναι μόνο σε ένα πεδίο. Όλες οι καθημερινές λειτουργίες είτε είναι οι πιο απλές είτε είναι οι πιο σύνθετες ενδέχεται από πίσω να τρέχουνε κάποιο ΙοΤ αυτοματισμό. Δεν νοείτε ότι χρειάζεται ιδιαίτερη μνεία αν με αυτό το τρόπο ξεπερνάμε κάποιους σκόπελους που σε προηγούμενα χρόνια ήταν αδιανόητο τεχνικά κάποια πράγματα να

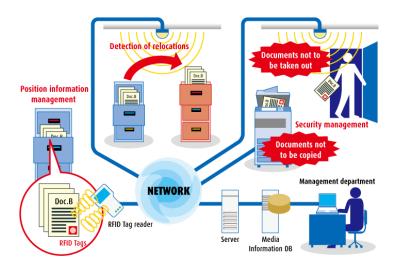

υλοποιηθούν, π.χ. η παρακολούθηση της αρτηριακής πίεσης από αυτοκόλλητο ΙοΤ αισθητήριο σε πραγματικό χρόνο, ή τη χρήση ΙοΤ αισθητηρίου για την παρακολούθηση της διαδρομής αντικειμένου στην γραμμή παραγωγής ή και την παρακολούθηση της ακριβής θέσης ενός διαβαθμισμένου εγγράφου μέσα σε μια υπηρεσία και την αποτροπή της κλοπής ή της αδικαιολόγητης εξόδου του ή της παραποίησης του.

Σχήμα 4: Smart Document management σε γραφεία

Παραστατικά στο παρακάτω σχήμα θα δούμε ενδεικτικά τα διάφορα πεδία εφαρμογών των ΙοΤ στην καθημερινότητα.

Σχήμα 5: Πεδία εφαρμογών ΙοΤ τεχνολογίας<sup>4</sup>

\_

<sup>&</sup>lt;sup>4</sup> Πεδία εφαρμογών των ΙοΤ τεχνολογιών, <u>πηγή</u>

# Κεφάλαιο 30

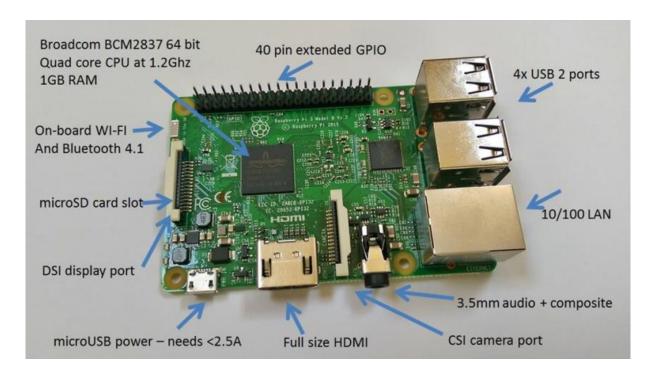

Στο κεφάλαιο **3°** περιγράφεται η αναπτυξιακή πλακέτα με τον μικροεπεξεργαστή Raspberry Pi και τι δυνατότητες έχει με τον έξω κόσμο και θα γίνει και μια εισαγωγή στον τρόπο χρήσης και παραμετροποίησης για το δικό μας σκοπό.

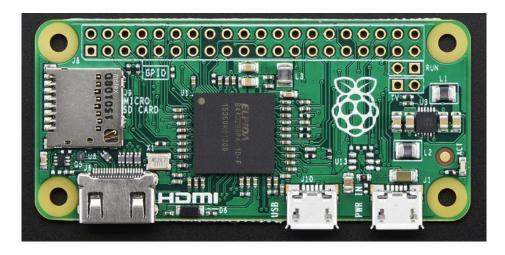

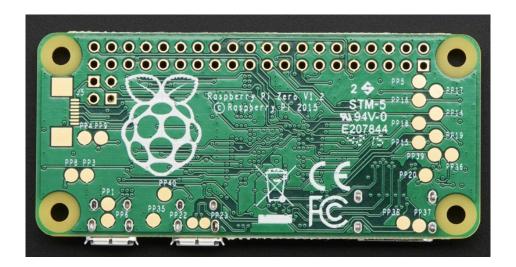

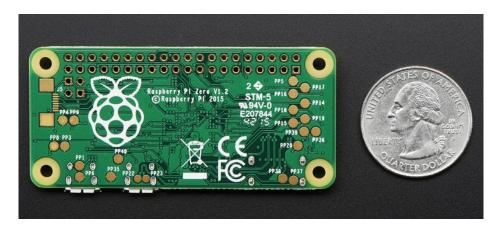

#### 3.1 Γνωριμία με το Raspberry Pi

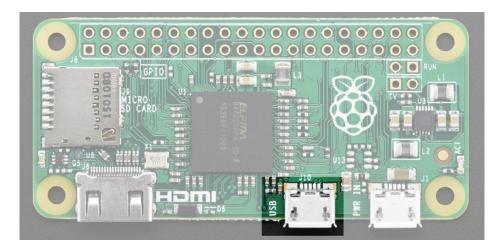

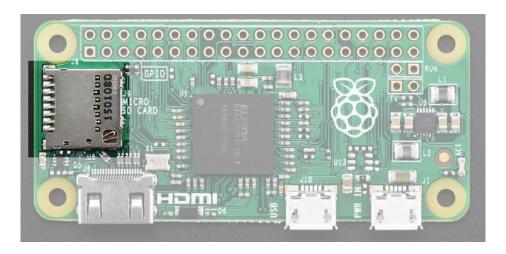

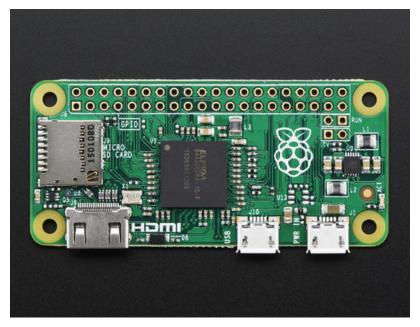

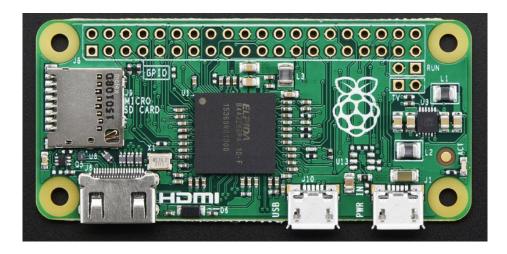

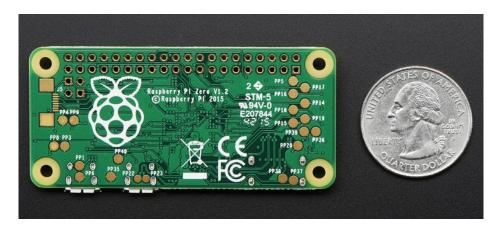

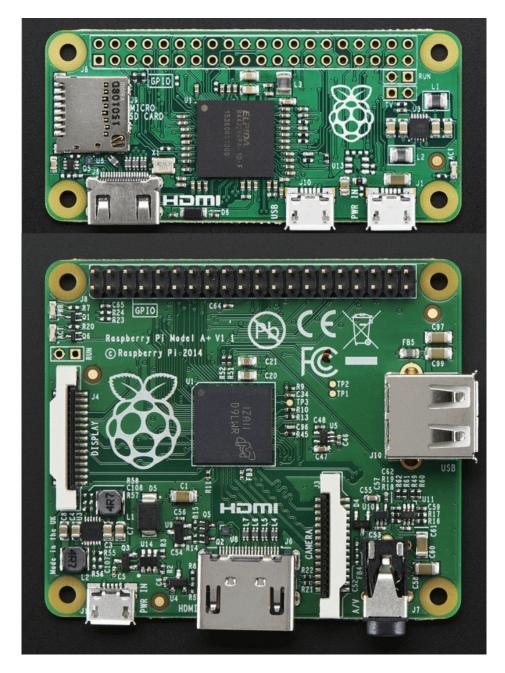

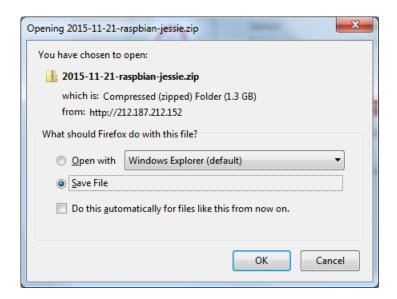

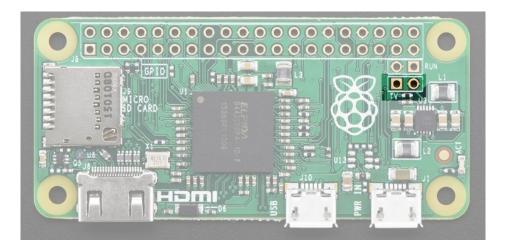

Το Raspberry Pi είναι ένας πλήρης υπολογιστής σε μέγεθος μιας πιστωτικής κάρτας.

Οι διάφορες γενιές του διαφέρουν στην ταχύτητα του επεξεργαστή και στην μνήμη που διαθέτουνε.

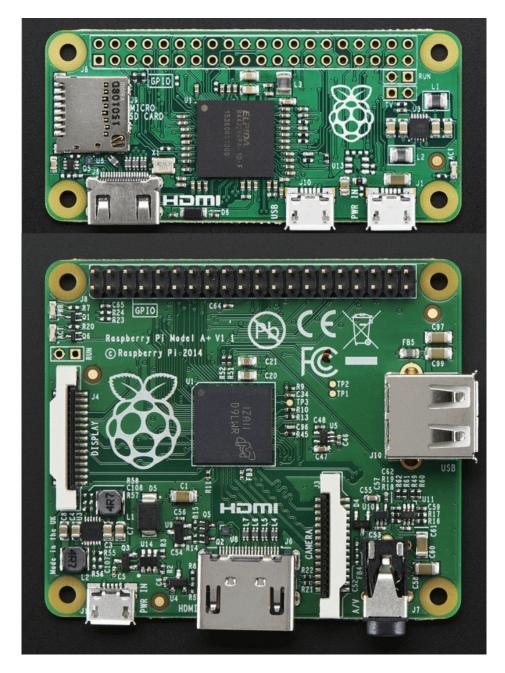

|                   | Raspberry Pi 3 Model B   | Raspberry Pi Zero   | Raspberry Pi 2 Model B  | Raspberry Pi Model B+ |

|-------------------|--------------------------|---------------------|-------------------------|-----------------------|

| Introduction Date | 2/29/2016                | 11/25/2015          | 2/2/2015                | 7/14/2014             |

| SoC               | BCM2837                  | BCM2835             | BCM2836                 | BCM2835               |

| CPU               | Quad Cortex A53 @ 1.2GHz | ARM11 @ 1GHz        | Quad Cortex A7 @ 900MHz | ARM11 @ 700MHz        |

| Instruction set   | ARMv8-A                  | ARMv6               | ARMv7-A                 | ARMv6                 |

| GPU               | 400MHz VideoCore IV      | 250MHz VideoCore IV | 250MHz VideoCore IV     | 250MHz VideoCore IV   |

| RAM               | 1GB SDRAM                | 512 MB SDRAM        | 1GB SDRAM               | 512MB SDRAM           |

| Storage           | micro-SD                 | micro-SD            | micro-SD                | micro-SD              |

| Ethernet          | 10/100                   | none                | 10/100                  | 10/100                |

| Wireless          | 802.11n / Bluetooth 4.0  | none                | none                    | none                  |

| Video Output      | HDMI / Composite         | HDMI / Composite    | HDMI / Composite        | HDMI / Composite      |

| Audio Output      | HDMI / Headphone         | HDMI                | HDMI / Headphone        | HDMI / Headphone      |

| GPIO              | 40                       | 40                  | 40                      | 40                    |

| Price             | \$35                     | \$5                 | \$35                    | \$35                  |

Σχήμα 6: Διάφορα μοντέλα Raspberry Pi και οι δυνατότητες τους

Το Raspberry Pi 3 (με το οποίο θα υλοποιήσουμε την παρούσα εργασία) διαθέτει έναν τετραπύρινο επεξεργαστή χρονισμένο στα 1.2GHz τεχνολογίας 64-Bit, με εσωτερική μνήμη 1GB RAM.

Για τη διασύνδεση με διάφορα περιφερειακά έχουμε στη διάθεση μας 4 θύρες USB 2.0 για σύνδεση με πληκτρολόγιο, ποντίκι και άλλα περιφερειακά, μια θύρα Ethernet ταχύτητας 10/100Mbps. Αυτό που το διακρίνει και το κάνει ιδιαίτερα δημοφιλή είναι η ενσωματωμένη δυνατότητα ασύρματης σύνδεσης τόσο σε Wifi όσο και με το πρωτόκολλο Bluetooth 4.1.

Επειδή είπαμε ότι πρόκειται για πλήρη υπολογιστή δεν θα πρέπει να ξεχάσουμε ότι διαθέτη έξοδο HDMI για την σύνδεση σε οθόνη Η/Υ (αν διαθέτει σύνδεση) ή ακόμη και στην σύνδεση σε τηλεοράσεις TFT/LCD. Όλο αυτό ολοκληρώνονται με τη δυνατότητα σύνδεσης ήχου στην

υποδοχή mini jack και τέλος microUSB υποδοχή για να την τροφοδοσία 5V με μέγιστο τα 2.5A.

Σχήμα 7: Raspberry Pi 3 model B

Για να λειτουργήσει το Pi 3 χρειάζεται και μια κάρτα microSD όπου θα εγκατασταθεί το λειτουργικό σύστημα γιατί από μόνο του δεν διαθέτει ενσωματωμένο λειτουργικό ούτε τρέχει με την ενεργοποίηση του κάποιο έτοιμο set ρουτίνων και κωδικών σε αντίθεση με το Arduino.

Ανάλογα με την χρήση του στις διάφορες υλοποιήσεις υπάρχουν έτοιμες διανομές λειτουργικού ανοιχτού κώδικα τις οποίες κυρίως χρησιμοποιούμαι ή ο χρήστης τις διαμορφώνει, τροποποιεί ή και εξελίσσει κατάλληλα για την χρήση του.

Το Raspberry Pi 3 αποτελεί ιδανική λύση για χρήση στην εκπαίδευση και την εκμάθηση προγραμματισμού διότι δίνετε από τους προγραμματιστές διάφορες εκδόσεις λειτουργικού με ανοιχτό κώδικα για την χρήση ή περ εταίρου παραμετροποίηση.

# <u>Κεφάλαιο 4°</u>

Στο κεφάλαιο  $4^{\circ}$  περιγράφονται αναλυτικά τα προ απαιτούμενα στάδια υλοποίησης για κάθε σημείο αναφοράς και παράδοσης του συστήματος με λεπτομερή επεξήγηση τόσο τεχνικά όσο και με εικόνες.

#### 4.1 Follow the Line με Raspberry Pi

Όπως γνωρίζουμε το Raspberry Pi έχει αμέτρητες εφαρμογές χάρη στην πλατφόρμα ανάπτυξης που βασίζετε ο επεξεργαστής ARM που περιέχει. Μια από αυτές είναι η δυνατότητα με χρήση κατάλληλων κυκλωματικών στοιχείων της παρακολούθησης γραμμής είτε το έχουμε σταθερά κάπου τοποθετημένο είτε το έχουμε σε μια αυτοκινούμενη κατασκευή.

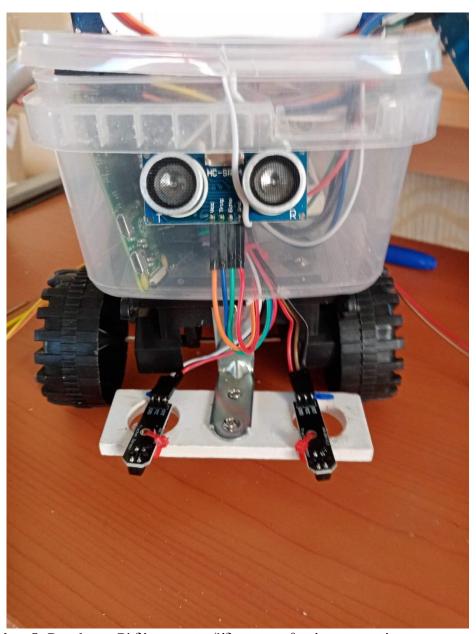

Σχήμα 8: Raspberry Pi δίτροχο αμαξίδιο με αισθητήρια για ανίχνευση γραμμής

#### 4.2 Λειτουργία και τεχνική ακολούθησης γραμμής (Line Follower)

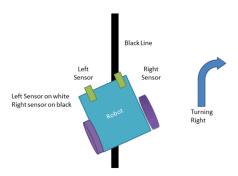

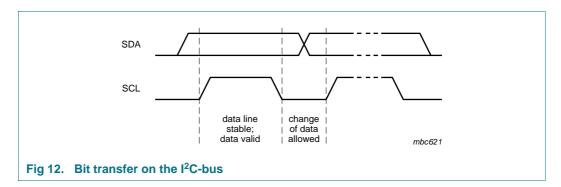

Η τεχνική που ακολουθείτε είναι ευρέως γνωστή σαν "Τεχνική ακολούθησης Γραμμής - Line Follower". Η αρχή στην οποία στηρίζετε όλη αυτή η τεχνική είναι ότι ένα ζευγάρι αισθητηρίων (μπορεί να γίνει και στην μπάντα των υπέρυθρων και στην μπάντα των ακουστικών σημάτων) ανιχνεύει την όδευση μιας προκαθορισμένης διαδρομής. Αυτή η διαδρομή μπορεί να είναι αόρατη οπότε έχουμε εκ των προτέρων εισάγει στο λογισμικό την ακριβή διαδρομή με σημεία αναφοράς (waypoints). Ή δε άλλη περίπτωση είναι η εμφανή οπτική παρακολούθηση μιας γραμμής (μαύρη στην πλειονότητα και χρωματιστή όπου χρειαστεί).

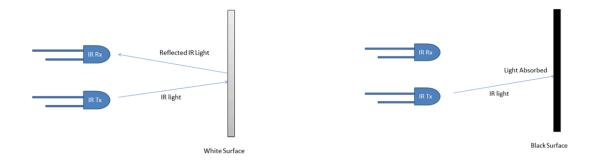

Στη δικιά μας περίπτωση θα χρησιμοποιήσουμε ένα ζευγάρι υπέρυθρων αισθητηρίων. Κάθε αισθητήριο έχει ένα ζευγάρι από πομποδέκτη IR. Ο πομπός εκπέμπει μια δέσμη φωτός στη μπάντα των υπέρυθρων το οποίο οδεύει προς τα μπρος. Εάν η δέσμη ανακλαστεί σε μια επιφάνεια θα υπάρξει επιστροφή και ο δέκτης που στη δικιά μας περίπτωση είναι μια φωτοδίοδος θα το αναγνωρίσει και θα δώσει σήμα στις επόμενες βαθμίδες του κυκλώματος.

Στη μπάντα των υπέρυθρων το φως ανακλάται από όλες τις επιφάνειες αλλά υπάρχουν 2 ακραίες καταστάσεις που μας βοηθούν ιδιαίτερα.

#### 1<sup>η</sup> περίπτωση:

Εάν η προσπίπτουσα επιφάνεια είναι άσπρη η ανάκλαση θα είναι ολική και θα ανιχνεύει ο δέκτης ισχυρό ΙR σήμα (Σχήμα 9α).

#### **2<sup>η</sup> περίπτωση:**

Εάν η προσπίπτουσα επιφάνεια είναι μαύρη η ανάκλαση θα είναι μηδενική γιατί θα έχει υποστεί ολική απορρόφηση της ΙΚ ακτινοβολίας (Σχήμα 9β).

Παραστατικά στο παρακάτω σχήμα βλέπουμε τις 2 καταστάσεις.

Σχήμα 9: α) με άσπρη ανακλώμενη επιφάνεια β) σε μαύρη ανακλώμενη επιφάνεια

Η λογική συνέχεια είναι πως θα αποτυπωθούν αυτές οι δυο προαναφερόμενες καταστάσεις κυκλωματικά.

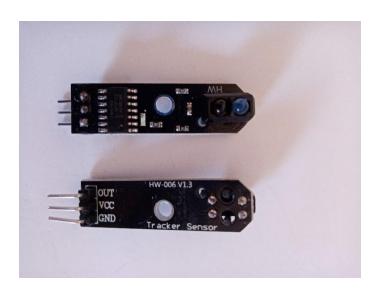

Στο παρακάτω σχήμα θα δούμε μια υλοποίηση σε πραγματική πλακέτα

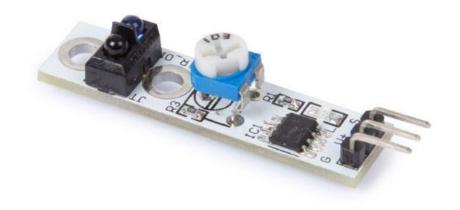

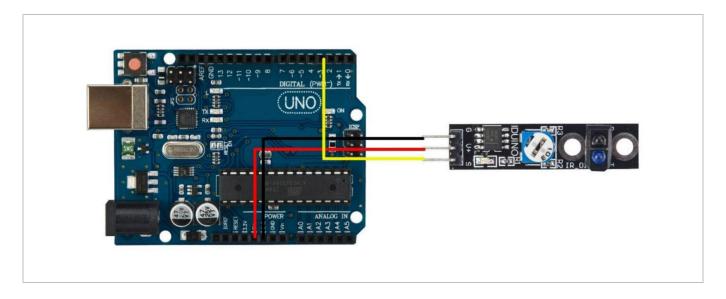

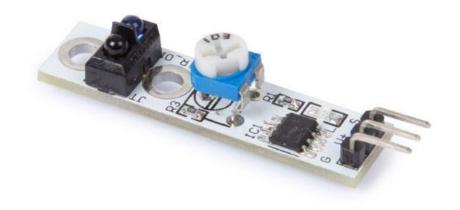

Σχήμα 10: ΙΚ αισθητήρες ΗW-006 για την υλοποίηση

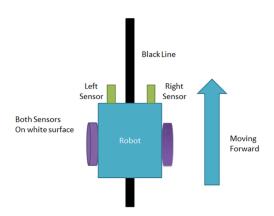

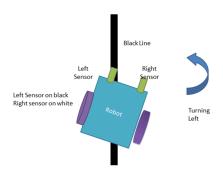

Βάση αυτής της αρχής και το τρόπο λειτουργίας στην παρούσα υλοποίηση θα χρησιμοποιήσουμε 2 ΙR αισθητήρες. Οι αισθητήρες είναι έτσι τοποθετημένοι σταθερά στο εμπρός τμήμα ώστε να ανιχνεύουν την πορεία του οχήματος. Το όχημα θα είναι εντός πορείας αν συνεχίζει να ανιχνεύει άσπρο από το ζευγάρι των αισθητηρίων. Σε περίπτωση που ανιχνεύσει μαύρο ένα από τα 2 αισθητήρια τότε θα υπάρχει πρόβλημα πορείας και θα πρέπει να επέλθει διόρθωση της πορείας.

Αν κανένας από τους 2 αισθητήρες ΙR δεν ανιχνεύει μαύρη γραμμή η εντολή από το λογισμικό είναι να προχωρήσει ευθεία.

Εάν το αριστερό αισθητήριο ανιχνεύσει μαύρο και το δεξί ανιχνεύει άσπρο τότε έχουμε πάτημα γραμμής από αριστερά και πρέπει να γίνει διόρθωση της πορείας προς τα αριστερά περιστρέφοντας το όχημα τόσο όσο να ανιχνεύσουν και τα 2 αισθητήρια πάλι άσπρο και να συνεχιστεί η ευθεία πορεία.

Εάν το δεξί αισθητήριο ανιχνεύσει μαύρο και το αριστερό ανιχνεύει άσπρο τότε έχουμε πάτημα γραμμής από δεξιά και πρέπει να γίνει διόρθωση της πορείας προς τα δεξιά περιστρέφοντας το όχημα τόσο όσο να ανιχνεύσουν και τα 2 αισθητήρια πάλι άσπρο και να συνεχιστεί η ευθεία πορεία.

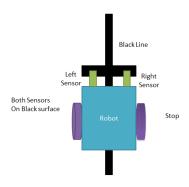

Κωδικοποιούμε την κατάσταση για σταμάτημα του οχήματος, δίνοντας στον κώδικα το απαιτούμενο έναυσμα για δέσμη ενεργειών όταν και τα 2 αισθητήρια αντιληφθούν μαύρη οριζόντια γραμμή, αυτό το πετυχαίνουμε με τη χρήση συνεχόμενης μαύρης γραμμής όπως φαίνετε και στο παρακάτω σχήμα (μπορεί να γίνει και με διακεκομμένη γραμμή αρκεί να είναι λίγο μεγαλύτερη από το πεδίο "όρασης" των αισθητηρίων).

Η όλη ανίχνευση γίνετε στα εξής στάδια.

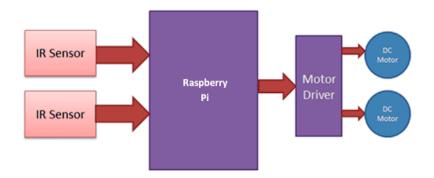

Τα 2 αισθητήρια IR ανιχνεύουν την πορεία και το εάν το όχημα βρίσκετε στην προκαθορισμένη ευθεία. Εκείνα με τη σειρά τους οδηγούνται σε ένα Raspberry Pi το οποίο με τον κατάλληλο

λογισμικό έχει προγραμματιστεί έτσι ώστε να ελέγχει και κινεί από κάθε πλευρά την αντίστοιχη ρόδα που με τη σειρά της διορθώνει την πορεία όπως προαναφέραμε. Μια άλλη απαίτηση είναι οι κινητήρες αυτοί να έχουν την δυνατότητα να κινούνται και προς τα μπρος και προς τα πίσω για να διορθώνουν την πορεία.

Σχήμα 11: Μπλοκ διάγραμμα οδήγησης των τροχών από τους ΙR αισθητήρες

Για αυτή την απλοϊκή υλοποίηση θα χρειαστούμε τα παρακάτω υλικά:

- Raspberry Pi 3 (καρδιά του συστήματος μας)

- IR Sensors (2 αισθητήρια IR)

- DC Gear Motor (2 βηματικούς κινητήρες για τους τροχούς του οχήματος)

- L293D Motor Driver

- Τροχοφόρο όχημα (ένα σασί από χαρτόνι ή όχημα από παροπλισμένο τηλεκατευθυνόμενο (ευχαριστώ το γιο μου για αυτό).

- Power bank (Πηγή τροφοδοσίας του συστήματος και των υπολοίπων υλικών)

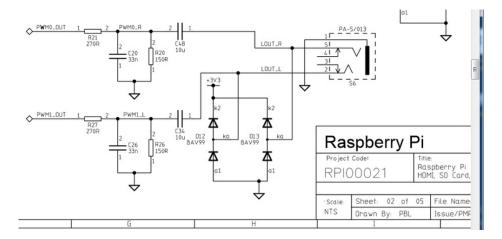

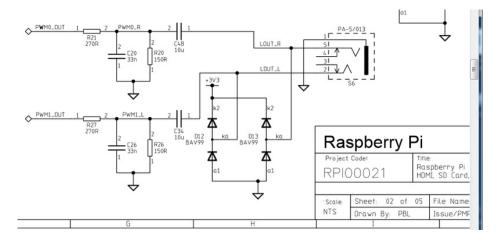

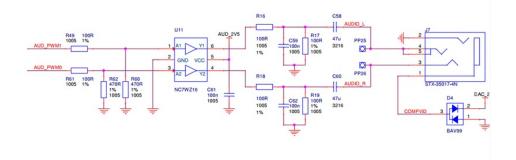

#### 4.3 Κυκλωματικό διάγραμμα για την ακολούθηση γραμμής

Παρακάτω θα επικεντρωθούμε στο κυκλωματικό διάγραμμα της υλοποίησης δίνοντας έμφαση στον τρόπο. Θα κάνουμε χρήση προγράμματος ανοικτού κώδικα για την υλοποίηση των κυκλωματικών διατάξεων βαθμίδα προς βαθμίδα επεξηγώντας επ' ακριβώς τον τρόπο λειτουργίας τους και στο τέλος θα παρουσιάσουμε την όλη διάταξη συγκεντρωτικά.

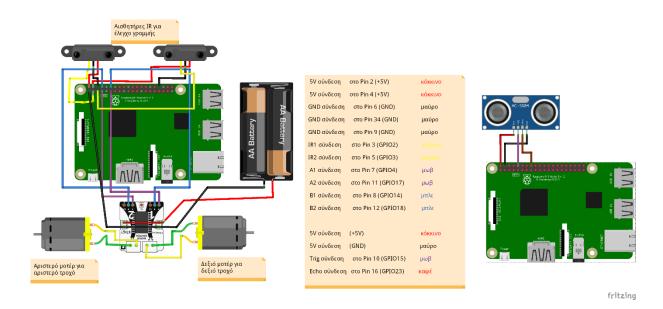

Το παρακάτω σχήμα είναι υλοποιημένο στο πρόγραμμα  $\mathbf{Fritzing}^5$  (ανοικτού κώδικα - πρότυπο σχέδιο υπάρχει ως σχέδιο με όνομα follow the line 1.fzz).

\_

<sup>&</sup>lt;sup>5</sup> Fritzing πρόγραμμα, https://fritzing.org/

Σχήμα 12: Follow the Line with Fritzing

Αναλυτικά όπως φαίνεται στο παραπάνω σχήμα στο κύκλωμα υπάρχουν 2 αισθητήρες IR και ένα ζευγάρι από DC μοτέρ που κινούν τους τροχούς ανεξάρτητα αριστερά και δεξιά. Το όλο κύκλωμα τροφοδοτείτε από μια συστοιχία από μπαταρίες ή ένα power bank για να δώσει τα απαιτούμενα 5V που χρειάζεται (στο σχήμα φαίνεται ως μπαταρία).

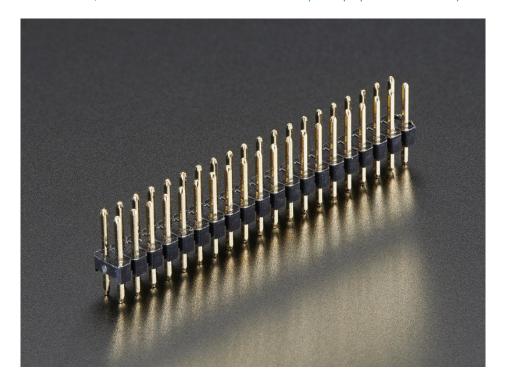

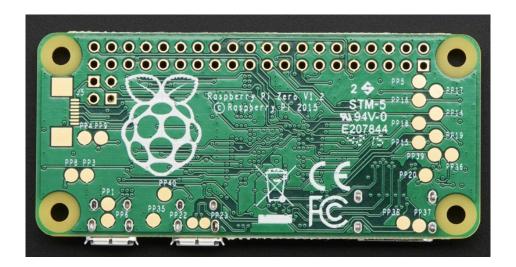

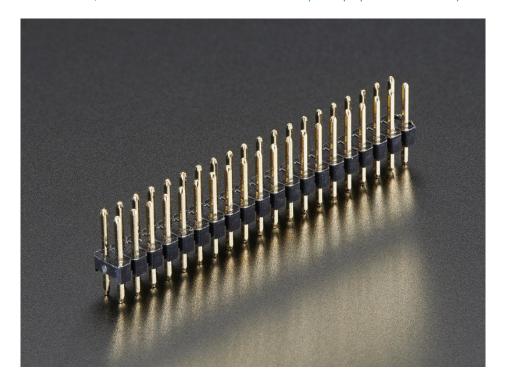

Επειδή κάθε έκδοση του Raspberry Pi έχει διαφορετική διάταξη στον connector σύνδεσης (δες παρακάτω σχήμα) θα πρέπει για καλύτερη κατανόηση θα δείξουμε αναλυτικά την διάταξη τους.

| Raspberry | Pi (R | ev1) |        | Raspberry | Pi (Re | ev 2) |        |   | Raspberry P | i B+, 2, | 3 & Zer | <u>o</u> |            |

|-----------|-------|------|--------|-----------|--------|-------|--------|---|-------------|----------|---------|----------|------------|

| 3V3       | 1     | 2    | 5V     | 3V3       | 1      | 2     | 5V     | 1 | 3V3         | 1        | 2       | 5V       | Key        |

| GPIOØ     | 3     | 4    | 5V     | GPIO2     | 3      | 4     | 5V     | 1 | GPIO2       | 3        | 4       | 5V       | +          |

| GPIO1     | 5     | 6    | GND    | GPIO3     | 5      | 6     | GND    | ] | GPIO3       | 5        | 6       | GND      | Ground     |

| GPIO4     | 7     | 8    | GPIO14 | GPIO4     | 7      | 8     | GPIO14 |   | GPIO4       | 7        | 8       | GPIO14   | UART       |

| GND       | 9     | 10   | GPIO15 | GND       | 9      | 10    | GPIO15 | ] | GND         | 9        | 10      | GPIO15   | I2C        |

| GPIO17    | 11    | 12   | GPIO18 | GPIO17    | 11     | 12    | GPIO18 |   | GPIO17      | 11       | 12      | GPIO18   | SPI        |

| GPIO27    | 13    | 14   | GND    | GPIO27    | 13     | 14    | GND    |   | GPIO27      | 13       | 14      | GND      | GPIO       |

| GPIO22    | 15    | 16   | GPIO23 | GPIO22    | 15     | 16    | GPIO23 |   | GPIO22      | 15       | 16      | GPIO23   | Pin Number |

| 3V3       | 17    | 18   | GPIO24 | 3V3       | 17     | 18    | GPIO24 |   | 3V3         | 17       | 18      | GPIO24   |            |

| GPIO10    | 19    | 20   | GND    | GPIO10    | 19     | 20    | GND    |   | GPIO10      | 19       | 20      | GND      |            |

| GPIO9     | 21    | 22   | GPIO25 | GPIO9     | 21     | 22    | GPIO25 |   | GPIO9       | 21       | 22      | GPIO25   |            |

| GPIO11    | 23    | 24   | GPI08  | GPIO11    | 23     | 24    | GPI08  |   | GPIO11      | 23       | 24      | GPIO8    |            |

| GND       | 25    | 26   | GPIO7  | GND       | 25     | 26    | GPIO7  |   | GND         | 25       | 26      | GPIO7    |            |

|           |       |      |        |           |        |       |        |   | DNC         | 27       | 28      | DNC      |            |

|           |       |      |        |           |        |       |        |   | GPIO5       | 29       | 30      | GND      |            |

|           |       |      |        |           |        |       |        |   | GPIO6       | 31       | 32      | GPIO12   |            |

|           |       |      |        |           |        |       |        |   | GPIO13      | 33       | 34      | GND      |            |

|           |       |      |        |           |        |       |        |   | GPIO19      | 35       | 36      | GPIO16   |            |

|           |       |      |        |           |        |       |        |   | GPIO26      | 37       | 38      | GPIO20   |            |

|           |       |      |        |           |        |       |        |   | GND         | 39       | 40      | GPIO21   |            |

Σχήμα 13: Διάταξη του GPIO Header στις διάφορες εκδόσεις Raspberry Pi

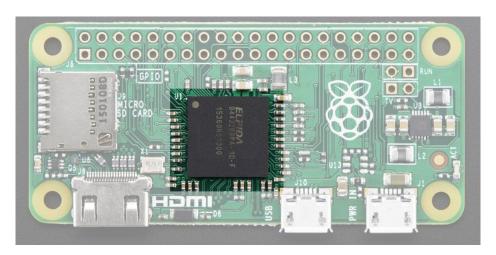

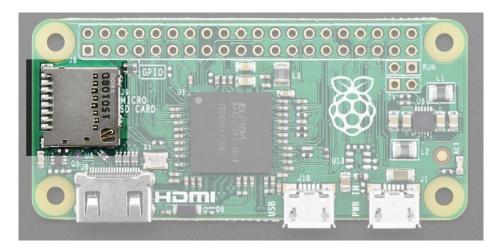

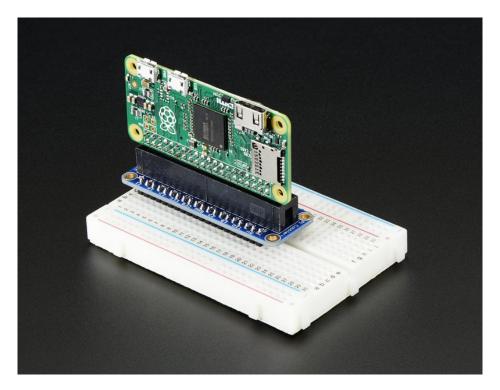

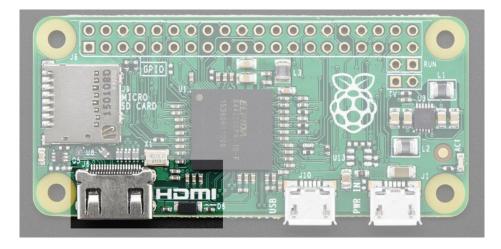

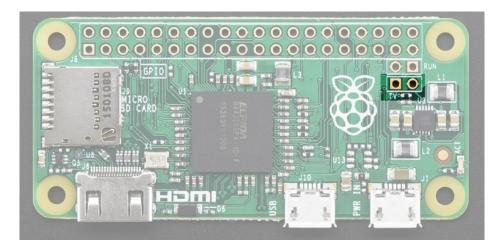

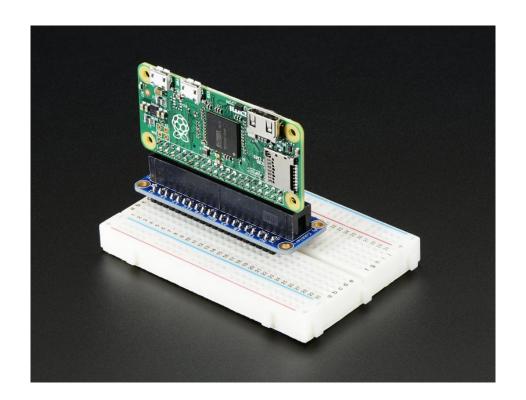

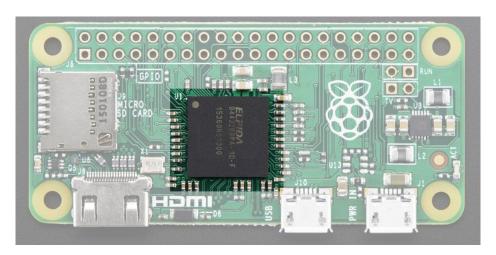

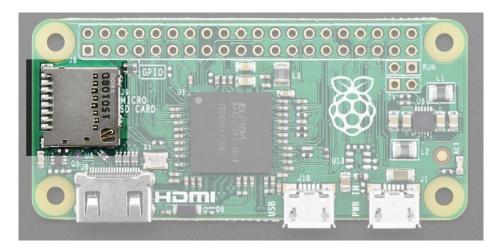

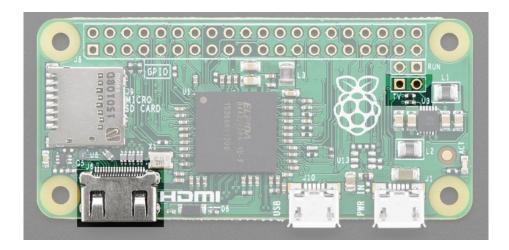

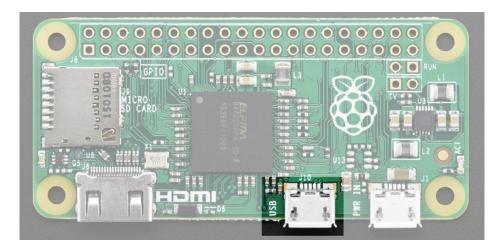

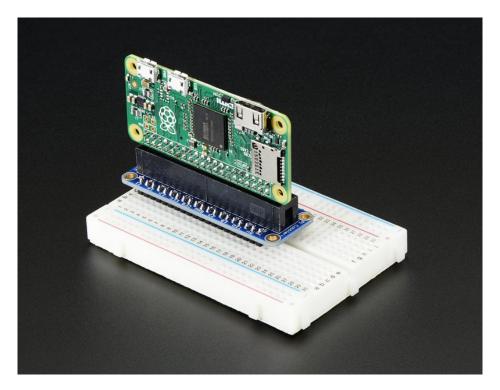

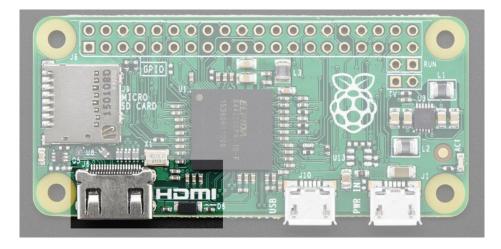

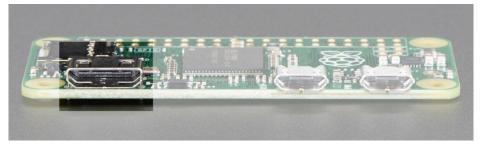

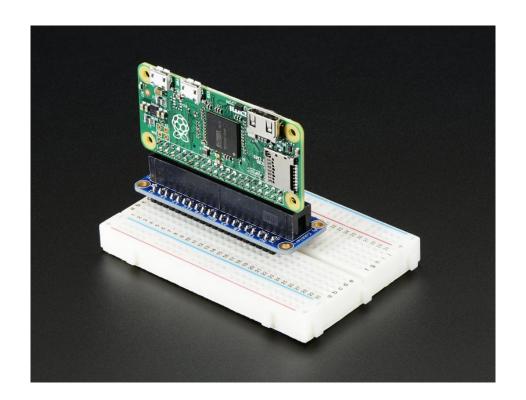

Στη δικιά μας υλοποίηση θα χρησιμοποιήσουμε το Raspberry Pi Zero v1.3 το οποίο είναι πιο οικονομικό (στα  $15 \in$ ) και έχει τις ίδιες δυνατότητες στο Header με το μεγάλο αδερφάκι του Raspberry Pi 3.

Σχήμα 14: Raspberry Pi Zero v1.3 vs v1.1

Οι ακροδέκτες 2 και 4 είναι για να τροφοδοτήσουν τα αισθητήρια IR με τα απαιτούμενα +5V(κόκκινοι αγωγοί). Στη συνέχεια γειώνουμε τα ίδια αισθητήρια IR στις θέσεις 6 και 34 (μαύρη σύνδεση). Με κίτρινο συνδέουμε τις εξόδους των αισθητήρων IR1 – pin 3 (GPIO2) και IR2 – pin 5 (GPIO3). Οι συνδέσεις αυτές θα μας χρειαστούν στην σύνταξη πιο κάτω του προγράμματος για την αναγνώριση της μαύρης γραμμής.

Για την οδήγηση των μοτέρ θα χρησιμοποιήσουμε 4 pins (μωβ το A και μπλε το B) αυτά συνδέονται με τα pins του Raspberry GPIO4 (pin7), GPIO14 (pin8), GPIO17 (pin11) και GPIO18 (pin12).Το πορτοκαλί και κίτρινο ζευγάρι καλωδίων αποτελούν το ζευγάρι σύνδεσης του εκάστοτε μοτέρ. Οι σύνδεση τους γίνετε από μια πλακέτα οδήγησης L293D που τροφοδοτείτε αντίστοιχα από μια πηγή τροφοδοσίας( μπαταρίες ή power bank). Η άνοδος θα τροφοδοτήσει την πλακέτα οδήγησης και η κάθοδος της τροφοδοσίας θα πάει στον κονέκτορα μας στη γείωση (pin 9) για να κλείσει το κύκλωμα.

| 5V σύνδεση    | στο <b>Pin 2</b>  | (+5V)   | κόκκινο |

|---------------|-------------------|---------|---------|

|               | στο <b>Pin 4</b>  | (+5V)   | κόκκινο |

| ❖ GND σύνδεση | στο <b>Pin 6</b>  | (GND)   | μαύρο   |

| ❖ GND σύνδεση | στο <b>Pin 34</b> | (GND)   | μαύρο   |

| ❖ GND σύνδεση | στο <b>Pin 9</b>  | (GND)   | μαύρο   |

| IR1 σύνδεση   | στο <b>Pin 3</b>  | (GPIO2) | κίτρινο |

| IR2 σύνδεση   | στο <b>Pin 5</b>  | (GPIO3) | κίτρινο |

| * | Α1 σύνδεση | στο <b>Pin 7</b>  | (GPIO4)           | μωβ  |

|---|------------|-------------------|-------------------|------|

| * | Α2 σύνδεση | στο <b>Pin 11</b> | ( <b>GPIO17</b> ) | μωβ  |

| * | Β1 σύνδεση | στο <b>Pin 8</b>  | ( <b>GPIO14</b> ) | μπλε |

| * | Β2 σύνδεση | στο <b>Pin 12</b> | ( <b>GPIO18</b> ) | μπλε |

# 4.4 Προγραμματισμός για την ρουτίνα για την ακολούθηση γραμμής

Μετά την επιτυχή σύνδεση της πλακέτας με τα υπόλοιπα κυκλωματικά στοιχεία η υλοποίηση θα είναι κάπως έτσι:

Σχήμα 15: Έτοιμο όχημα για την υλοποίηση Follow the Line

Το επόμενο βήμα είναι ο προγραμματισμός των ρουτίνων για να υλοποιήσουμε το Follow the Line Αλγόριθμο γραμμένο σε έκδοση Python.

Στην παρούσα διπλωματική δεν θα επεκταθούμε ούτε θα αναλύσουμε τους τρόπους προγραμματισμού σε περιβάλλον Python $^6$ . Θα θεωρηθεί ότι ο αναγνώστης θα ανατρέξει σε

\_

<sup>&</sup>lt;sup>6</sup> Python programming language

βιβλιογραφία και παραδείγματα του τρόπου προγραμματισμού σε αυτή τη γλώσσα προγραμματισμού.

Προχωράμε στην υλοποίηση.

Άρα πρώτα εισάγουμε από την βιβλιοθήκη για να ενεργοποιηθεί ο προγραμματισμός των ακροδεκτών της σύνδεσης GPIO στο Raspberry Pi. Για λόγους συντομίας θα κωδικοποιήσουμε τον όρο "GPIO" σε "ΙΟ" για να έχουμε μια ποιο σαφή εικόνα κατά τον προγραμματισμό.

# import RPi.GPIO as GPIO # calling header file for GPIO's of PI

Για να αποφύγουμε λάθη στον προγραμματισμό των ακροδεκτών θα βάλουμε μια εντολή να αγνοήσει αυτό το πρόβλημα και να προχωρήσει με την εκτέλεση του προγράμματος εξόδου αν έχει.

#### GPIO.setwarnings (False)

Μπορούμε να αναφερθούμε όπως και στον προγραμματισμό σε Arduino είτε με τον αριθμό του ακροδέκτη είτε με την ιδιότητα που έχει το συγκεκριμένο pin (π.χ. PIN8 που είναι το GPIO14).

#### GPIO.setmode (GPIO.BOARD)

Πρέπει στη συνέχεια να ορίσουμε 2 ακροδέκτες ως είσοδοι σημάτων και 4 ακροδέκτες ως εξόδους. Τα πρώτα 2 θα είναι οι είσοδοι από τους αισθητήρες IR ενώ οι άλλοι 4 είναι ανά δυο για τον έλεγχο των τροχών αριστερά και δεξιά (Η διάταξη των μοτέρ 1 και 2 είναι όπως φαίνονται στο σχήμα).

```

GPIO.setup(3,GPIO.IN) #GPIO2 \rightarrow IR1 έξοδος GPIO.setup(5,GPIO.IN) #GPIO3 \rightarrow IR2 έξοδος

```

```

GPIO.setup(7,GPIO.OUT) #GPIO4 \rightarrow κινητήρας1 (δεξιά) θέση A IO.setup(8,GPIO.OUT) #GPIO14 \rightarrow κινητήρας1 (δεξιά) θέση B

```

```

GPIO.setup(11,GPIO.OUT) #GPIO17 \rightarrow κινητήρας2 (αριστερά) θέση A GPIO.setup(12,GPIO.OUT) #GPIO18 \rightarrow κινητήρας2 (αριστερά) θέση B

```

Τα υπέρυθρα αισθητήρια δίνουν έξοδο «αληθής» όσο ανιχνεύουν άσπρη επιφάνεια. Ως επακόλουθο όταν και οι δυο αισθητήρες μας δίνουν αληθής αποτέλεσμα μπορούμε να οδηγήσουμε το όχημα μας να προχωρήσει ευθεία. Οι ρουτίνες είναι οι εξής:

if(GPIO.input(3)==True and GPIO.input(5)==True): #άσπρη επιφάνεια και ευθεία πορεία

```

GPIO.output (4,True) #1A+

GPIO.output (14,False) #1B-

GPIO.output (17,True) #2A+

GPIO.output (18,False) #2B-

```

Εάν τώρα βρεθεί ο αριστερός αισθητήρας να ανιχνεύει μαύρη γραμμή θα πρέπει να κάνουμε στροφή προς τα αριστερά. Θα πρέπει να σταματήσει ο δεξιός κινητήρας και να γυρίσει ο αριστερός έως ότου σταματήσει η ανίχνευση της μαύρης γραμμής.

```

elif(GPIO.input(3)==False and GPIO.input(5)==True): #στροφή προς τα αριστερά

```

```

GPIO.output (4,True) #1A+

GPIO.output (14,True) #1B-

GPIO.output (17,True) #2A+

GPIO.output (18,False) #2B-

```

Σε αντιδιαστολή αν ανιχνεύσουμε δεξιά μαύρη γραμμή και αριστερά άσπρο θα πρέπει το όχημα μας να κάνει στροφή προς τα δεξιά. Ο κώδικας είναι:

```

elif(GPIO.input(3)==True and GPIO.input(5)==False): #στροφή προς τα δεξιά

```

| GPIO.output(4,True)   | #1A+ |

|-----------------------|------|

| GPIO.output(14,False) | #1B- |

| GPIO.output(17,True)  | #2A+ |

| GPIO.output(18,True)  | #2B- |

Αν και οι 2 αισθητήρες πατήσουν μαύρη γραμμή τότε το όχημα μας θα πρέπει να σταματήσει να κινείται γιατί θα είμαστε σε θέση που απαιτεί να καλέσουμε κάποια υπορουτίνα.

```

else: #σταμάτημα του οχήματος

```

| GPIO.output(4,True)  | <i>#1A</i> + |

|----------------------|--------------|

| GPIO.output(14,True) | #1B-         |

| GPIO.output(17,True) | #2A+         |

| GPIO.output(18,True) | #2B-         |

#### 4.5 Τροχοφόρο όχημα σε κίνηση με αλγόριθμο ανίχνευσης γραμμής

Ο ολοκληρωμένος κώδικας για το τροχοφόρο όχημα σε κίνηση με τον αλγόριθμο ανίχνευσης γραμμής για την ρουτίνα "Follow the Black Line" είναι ο παρακάτω:

import RPi.GPIO as GPIO # calling header file for GPIO's of PI

**GPIO.setwarnings(False)**

GPIO.setmode (GPIO.BOARD) # The Rpi uses the physical pin numbering

# setup pins as Inputs and Outputs

GPIO.setup(3,GPIO.IN) #GPIO2 IR1 έξοδος GPIO.setup(5,GPIO.IN) #GPIO3 IR2 έξοδος

GPIO.setup(7,GPIO.OUT) #GPIO4 κινητήρας 1 (δεξιά) θέση A GPIO.setup(8,GPIO.OUT) #GPIO14 κινητήρας 1 (δεξιά) θέση B

GPIO.setup(11,GPIO.OUT) #GPIO17 κινητήρας 2 (αριστερά) θέση Α

# GPIO.setup(12,GPIO.OUT) #GPIO18

κινητήρας 2 (αριστερά) θέση Β

#### while 1:

if(GPIO.input(3)==True and GPIO.input(5)==True): #άσπρη επιφάνεια και ευθεία πορεία

| GPIO.output(4,True)   | #1A |

|-----------------------|-----|

| GPIO.output(14,False) | #1B |

| GPIO.output(17,True)  | #2A |

| GPIO.output(18,False) | #2B |

elif(GPIO.input(3)==False and GPIO.input(5)==True): #στροφή προς τα αριστερά

| GPIO.output(4,True)   | #1A |

|-----------------------|-----|

| GPIO.output(14,True)  | #1B |

| GPIO.output(17,True)  | #2A |

| GPIO.output(18,False) | #2B |

elif(GPIO.input(3)==True and GPIO.input(5)==False): #στροφή προς τα δεξιά

| <b>GPIO.output(4,True)</b>   | #1A |

|------------------------------|-----|

| <b>GPIO.output(14,False)</b> | #1B |

| <b>GPIO.output(17,True)</b>  | #2A |

| <b>GPIO.output(18,True)</b>  | #2B |

else: #σταμάτημα του οχήματος

GPIO.output(4,True) #1A GPIO.output(14,True) #1B GPIO.output(17,True) #2A GPIO.output(18,True) #2B

Ο πλήρης κώδικας για όλη την διάταξη που υλοποιήθηκε υπάρχει στην αρχή του κεφαλαίου 6.

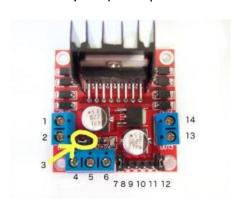

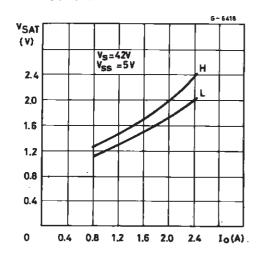

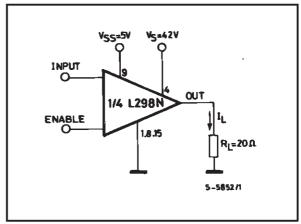

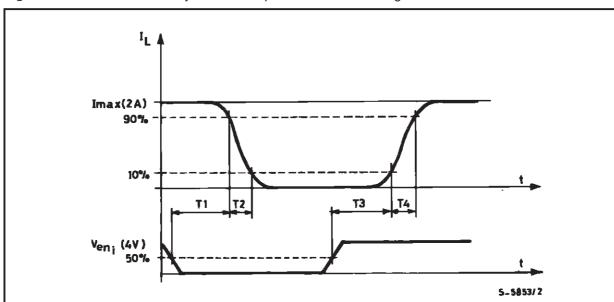

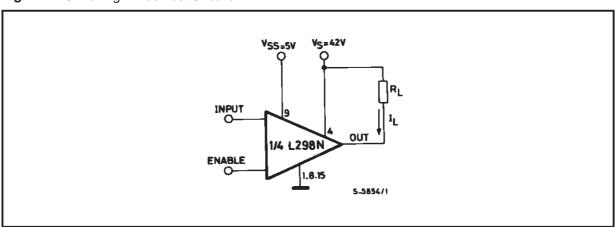

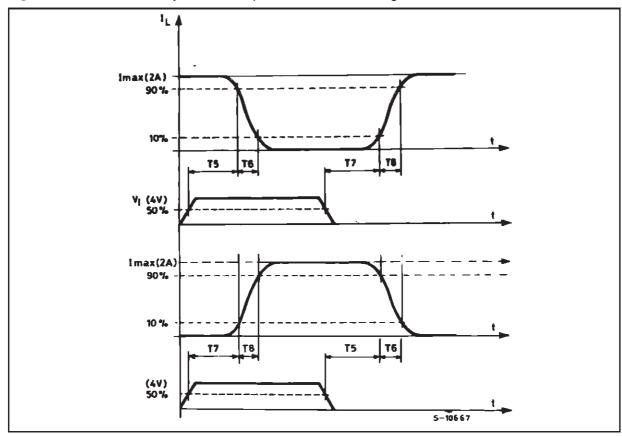

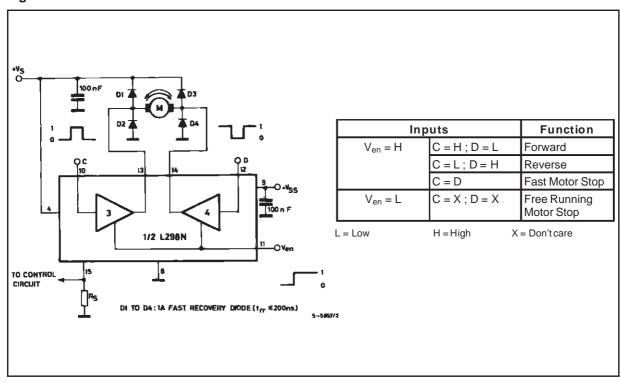

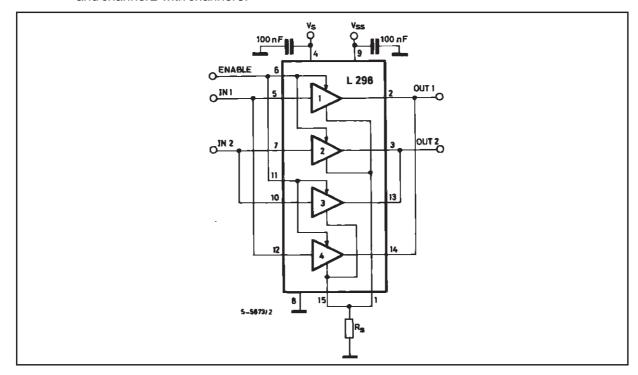

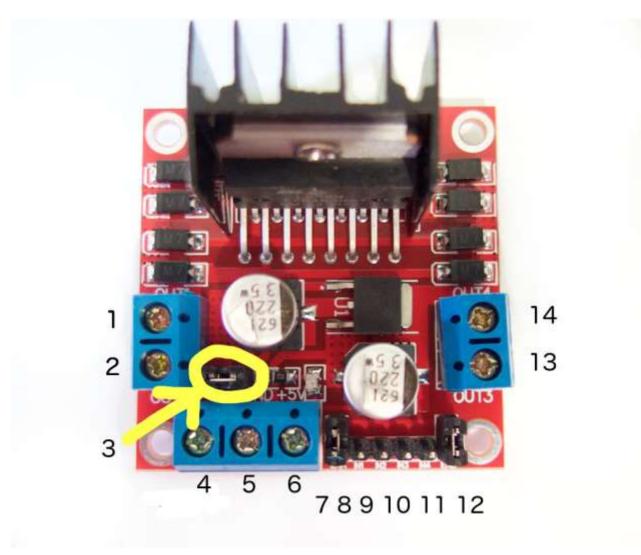

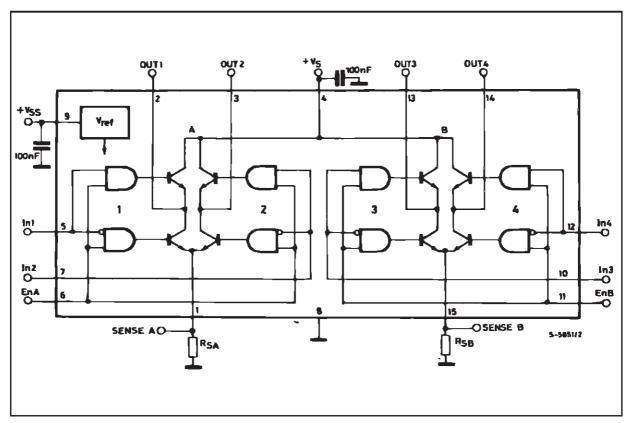

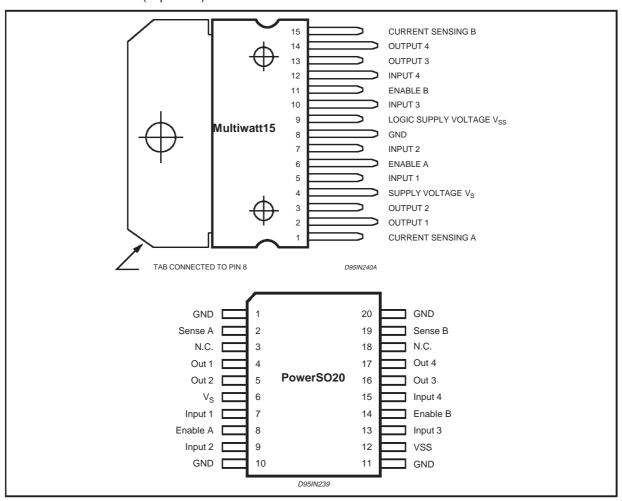

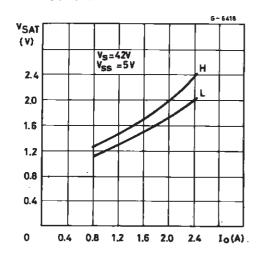

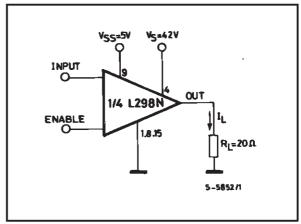

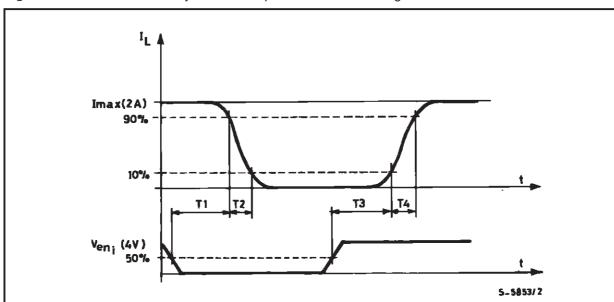

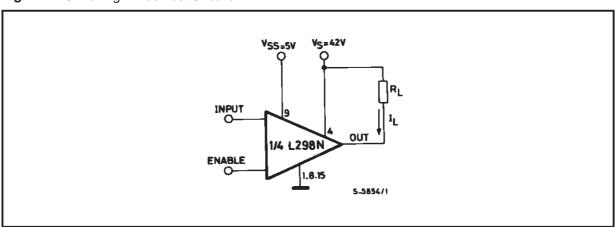

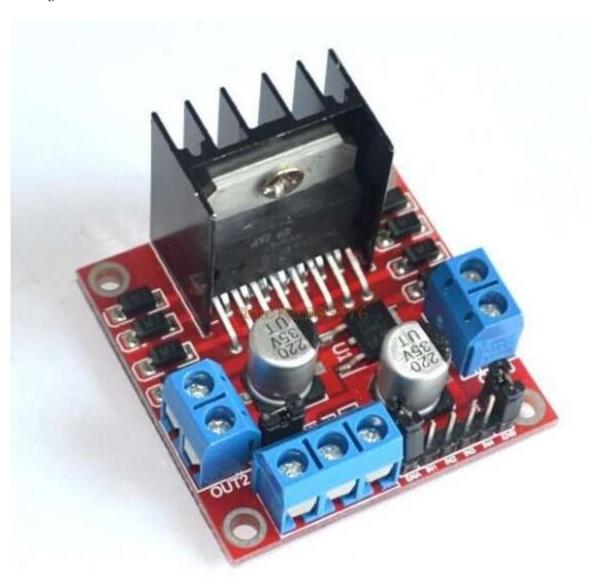

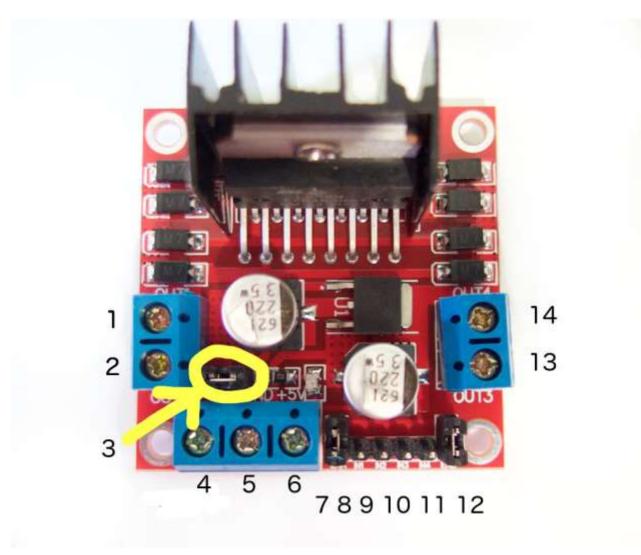

Η Συνδεσμολογία στην πλακέτα είναι η παρακάτω<sup>7</sup>:

<sup>&</sup>lt;sup>7</sup> Official connection description for L298N Motor Driver

- 1. DC motor 1 "+" or stepper motor A+

- 2. DC motor 1 "-" or stepper motor A-

- 3. 12V jumper **remove this if using a supply voltage greater than 12V DC**. This enables power to the onboard 5V regulator

- 4. Connect your motor supply voltage here, maximum of 35V DC. Remove 12V jumper if >12V DC

- 5. GND

- 6. 5V output if 12V jumper in place, ideal for powering your Arduino (etc)

- 7. DC motor 1 enable jumper. Leave this in place when using a stepper motor. Connect to PWM output for DC motor speed control.

- 8. IN1

- 9. IN2

- 10. IN3

- 11. IN4

- 12. DC motor 2 enable jumper. Leave this in place when using a stepper motor. Connect to PWM output for DC motor speed control.

- 13. DC motor 2 "+" or stepper motor B+

- 14. DC motor 2 "-" or stepper motor B-

Και μια καλύτερη εικόνα του ίδιου

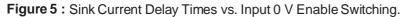

Σχήμα 16: L298 Motor Driver

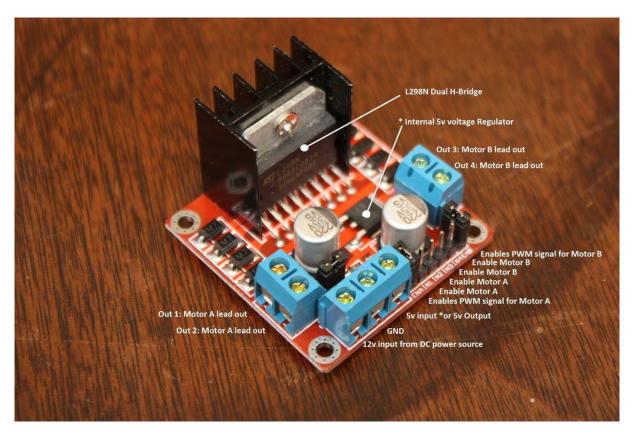

Φορτώνοντας τον κώδικα τώρα στο Raspberry Pi και δίνοντας του μια δοκιμαστική διαδρομή θα έχουμε το επιθυμητό αποτέλεσμα να κινείται με ευκολία στην προδιαγεγραμμένη διαδρομή.

Η παρούσα διαδρομή έχει σχεδιαστεί και εκτυπωθεί από ένα έτοιμο free downloadable project του  $Github^8$ .

Για αυτό το σκοπό εφαρμόσαμε μια δοκιμαστική διαδρομή και αφήσαμε το τροχοφόρο όχημα να κινείται πάνω σε αυτή.

Θα χρειαστούμε για την δικιά μας διαδρομή τα εξής κομμάτια για να την συνθέσουμε:

- 9 x το κομμάτι με αριθμό 3 (στροφή)

- 6 x το κομμάτι με αριθμό 2 (ευθεία)

- 1 x το κομμάτι με αριθμό 12 (στροφή και ευθεία)

- 1 x το κομμάτι με αριθμό 22 (εκκίνηση)

- 4 x το κομμάτι με αριθμό 18 (ευθεία με σημείο αναφοράς)

Η διαδρομή θα έχει την παρακάτω μορφή μαζί με τα 4 σημεία αναφοράς (waypoints)

Σχήμα 17: Εικονική δοκιμαστική διαδρομή

<sup>&</sup>lt;sup>8</sup> The Raspberry Project Guy

Σχήμα 18: Πραγματική δοκιμαστική διαδρομή Διαστάσεων 2m x 0.7m με σημεία αναφοράς 1 έως 4

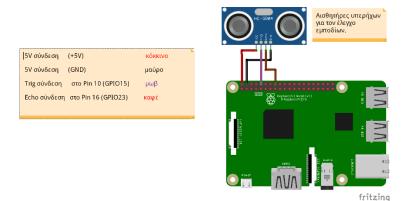

Επίσης σε αυτή τη διάταξη θα δούμε ότι έχουμε ενσωματώσει και έναν αισθητήρα υπερήχων (HC-SR04).

Σχήμα 19: Αισθητήρας υπερήχων HC-SR04

Σκοπός του είναι να ανιχνεύει προς τα εμπρός την παρουσία ή όχι εμποδίων, ώστε είτε να σταματήσει το όχημα (που θα υλοποιήσουμε) ή να εκτελέσει έναν πιο πολύπλοκο αλγόριθμο αποφυγής εμποδίου όταν αυτός έχει ενσωματωθεί κατάλληλα στον κώδικα.

Η αρχή λειτουργίας φαίνεται στο παρακάτω σχήμα.

Σχήμα 20: Αρχή λειτουργίας Ultrasonic Sensor

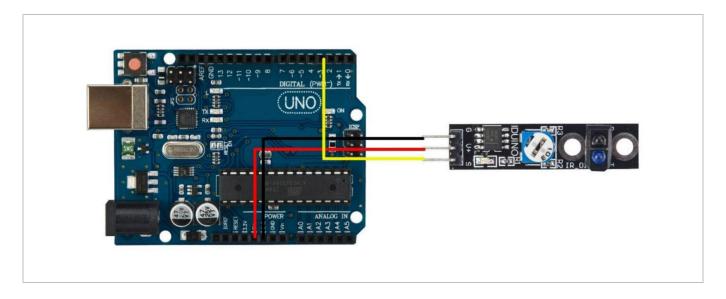

Ο αισθητήρας έχει 4 pins:

| • | VCC  | 5V Supply                    | κόκκινο |

|---|------|------------------------------|---------|

| • | TRIG | Trigger Input pin16 (GPIO23) | καφέ    |

| • | Echo | Echo Input pin10 (GPIO15)    | μωβ     |

| • | GND  | Ground                       | μαύρο   |

Η συνδεσμολογία απαιτεί τροφοδοσία στα 5V την οποία του παρέχουμε ήδη από το υπόλοιπο κύκλωμα σύνδεσης «**Follow the Line**». Το pin Echo δεν πρέπει να συνδεθεί κατευθείαν σε είσοδο Pin του Raspberry Pi γιατί αλλιώς θα κάψει την είσοδο. Για να μην το κάνει αυτό θα χρησιμοποιήσουμε έναν διαιρέτη τάσης ώστε να αποφύγουμε τα προαναφερόμενα.

Ένα απόσπασμα του κώδικα είναι το παρακάτω όπου ορίζουμε το pin16 ως είσοδο του παλμού Trigger από τον αισθητήρα υπερήχων και το pin10 ως είσοδο του παλμού Echo.

Παραστατικά βλέπουμε και το παρακάτω σχέδιο με τις συνδέσεις στο Fritzing (ultrasonic HC-SR04 thesis.fzz).

Σχήμα 21: Σύνδεση του αισθητήρα υπερήχων HC-SR04 στο Raspberry

Η συνδεσμολογία είναι συνέχεια του προηγούμενου κυκλώματος και δεν αποτελεί ξεχωριστή οντότητα όπως όλα τα σχέδια σε αυτή τη διπλωματική.

Αναδεικνύουμε κάθε φορά το επιμέρους κύκλωμα μαζί με τις επεξηγήσεις για να αποτυπώσουμε πως δουλεύει και πως είναι ο κώδικας για να λειτουργήσει.

Ο κώδικας σε Python είναι:

# We setup the pins as Inputs and Outputs for controlling the Ultrasonic Sensor for

# obstacle avoidance

GPIO.setup(10,GPIO.IN) #TRIGGER PULSE

GPIO.setup(16,GPIO.IN) #ECHO PULSE

sensor = DistanceSensor(echo=16, trigger=10, max\_distance=1, threshold\_distance=0.2)

led = LED(30)

sensor.when\_in\_range = led.on #turns led on when sensor in range

sensor.when\_out\_of\_range = led.off #turns led off when sensor out of range

pause()

Όταν ο αισθητήρας ανιχνεύσει «εμπόδιο» μπροστά του και είναι σε απόσταση 20cm τότε ανάβει ένα κόκκινο Led το οποίο το έχουμε συνδέσει στην έξοδο στο pin 30.

Μια διαφοροποίηση αυτού του προγράμματος θα ήταν αφού ανιχνευτεί το εμπόδιο (το οποίο εμείς απλά βλέπουμε όσο είναι μπροστά μας) να σταματήσει και το όχημα, εκτός από το οπτικό σημάδι που θα ανάβει, για όσο διάστημα βρίσκετε μπροστά του να τρέξει και μια ρουτίνα αποφυγής ή ακόμα αποφυγής και συνέχισης της διαδρομής. Αυτό έχει και τα υπέρ και τα κατά του.

#### ҮПЕР:

- Το όχημα δεν μετακινείται όσο «βλέπει» μπροστά του εμπόδιο

- Δεν χρειάζεται επιπλέον πολύπλοκος κώδικας για την εξυπηρέτηση της ρουτίνας.

#### **KATA:**

• Πρέπει να δοθεί έναυσμα από τον κώδικα για τη συνέχιση του προγράμματος

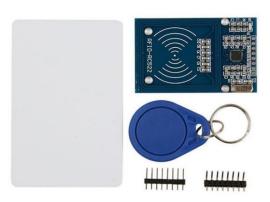

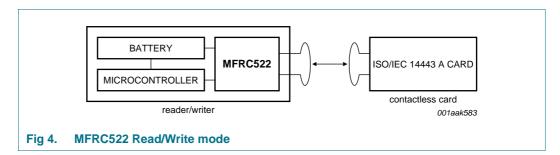

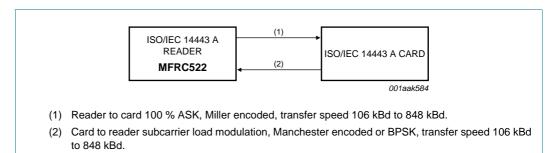

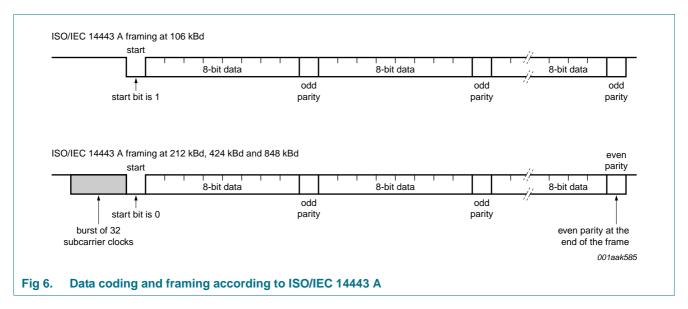

#### **4.6 RFID**

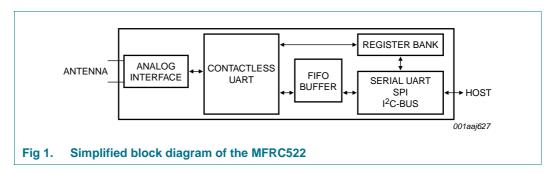

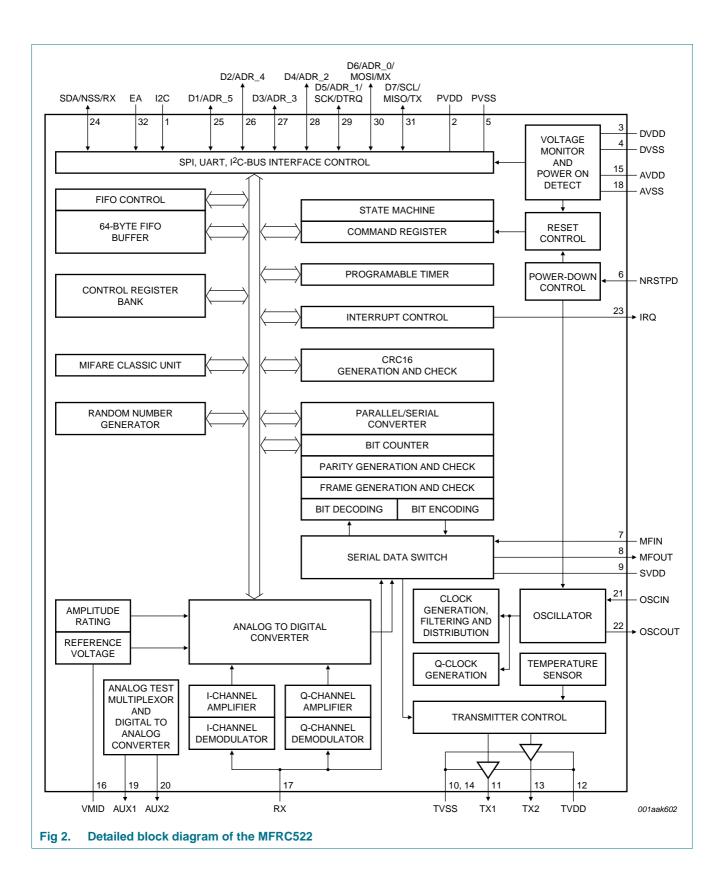

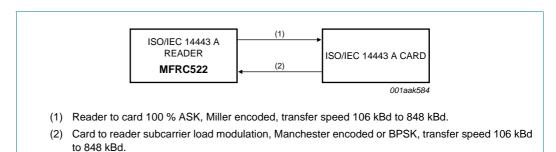

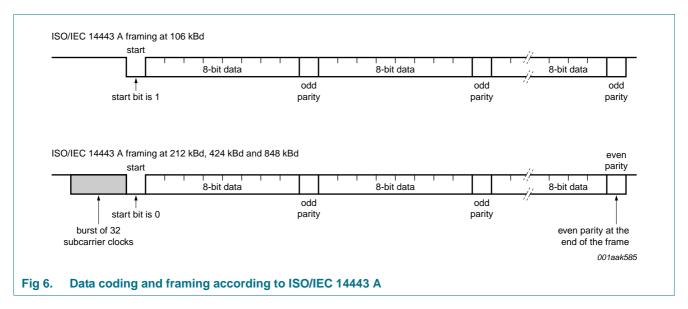

Οι ετικέτες RFID (**R**adio **F**requency **ID**entification) είναι μία πολλά υποσχόμενη και ταυτόχρονα ταχύτατα νέα αναπτυσσόμενη τεχνολογία. Τι είναι όμως οι ετικέτες RFID; Ουσιαστικά πρόκειται για μικροσκοπικά chips με ενσωματωμένη κεραία, τα οποία χρησιμοποιούνται ως αυτοκόλλητες ετικέτες σε διάφορα προϊόντα. Έτσι όταν βρεθούν κοντά σε μία συσκευή ανάγνωσης αυτής (RFID reader) εκπέμπουν τα δεδομένα που έχουν μέσα τους όπως, π.χ. την ταυτότητα του προϊόντος, την ημερομηνία κατασκευής ή παραγωγής ή κάποιο άλλο κωδικό που εμείς επιλέγουμε κ.τ.λ.

Σχήμα 22: RFID tags τύπου κάρτας και ετικέτας

Σήμερα για τη σήμανση των προϊόντων χρησιμοποιείται συνήθως για λόγους οικονομικούς και ευκολίας παγκοσμίως ο γραμμικός κώδικας (Barcode).

Γρήγορα όμως αυτός θα αντικατασταθεί από τον RFID, για τους εξής λόγους:

- 1. Δεν απαιτεί αυστηρή οπτική επαφή όπως γίνεται με το barcode. Για παράδειγμα στα εμπορικά καταστήματα (supermarket) κάθε προϊόν περνάει από ένα "μάτι" στο ταμείο για να "διαβαστεί" το barcode ώστε να αποτυπωθεί στην οθόνη του ταμείο το προϊόν και το κόστος του. Εάν δεν περάσει το εμπόρευμα περνάει απαρατήρητο και δεν θα χρεωθεί καν.

- 2. **Η ανάγνωση των στοιχείων γίνεται από απόσταση.** Η απόσταση του αναγνώστη είναι πολύ μεγαλύτερη από αυτή του barcode reader που είναι το πολύ κάποια εκατοστά.

- 3. **Αυξημένη ασφάλεια.** Τοποθετούνται σε σημεία που δεν γίνονται εύκολα αντιληπτά π.χ. μέσα στα ρούχα, στις ετικέτες ή στο εσωτερικό διαφόρων προϊόντων ή και συσκευασιών.

- 4. Οι συσκευές ανάγνωσης των RFID tags μπορούν να τοποθετηθούν στην οροφή, στο δάπεδο, σε σημεία αναφοράς κτλ. Οι συσκευές αυτές είναι μικροπομποί, οι οποίοι δημιουργούν ένα ηλεκτρομαγνητικό πεδίο. Έτσι μόλις περάσει από μέσα τους το προϊόν, ενεργοποιείται η ετικέτα και μεταδίδει τις πληροφορίες της πίσω στον μικροπομπό.

- 5. Δεν χρειάζονται μπαταρίες για την λειτουργία τους.

Θα μπορούσαμε να πούμε ότι η τεχνολογία αυτή έχει απεριόριστα πεδία εφαρμογών. Με την ανθρώπινη φαντασία μπορεί να βρούμε και νέα πεδία εφαρμογών. Τέτοια πεδία κάνουν ήδη εφαρμογή αυτής της τεχνολογίας και είναι κάποια από τα παρακάτω όπως:

- Σήμανση ζώων για εντοπισμό τους ή και την άντληση στοιχείων

- Αντικλεπτικά συστήματα θυρών

- Βιβλιοθήκες, παρακολούθηση κίνησης βιβλίων

- Αεροδρόμια, ανίχνευση μετακίνησης αποσκευών

- Κάρτες ανέπαφων συναλλαγών (πιστωτικές/χρεωστικές κάρτες)

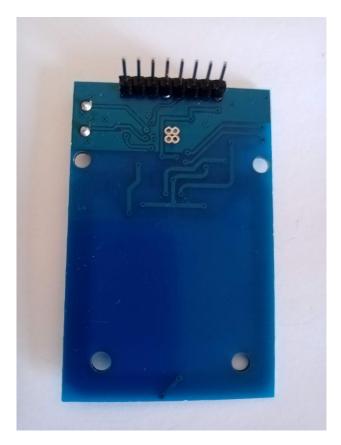

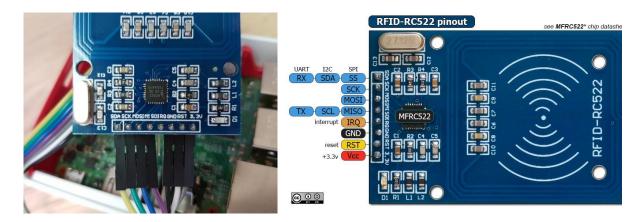

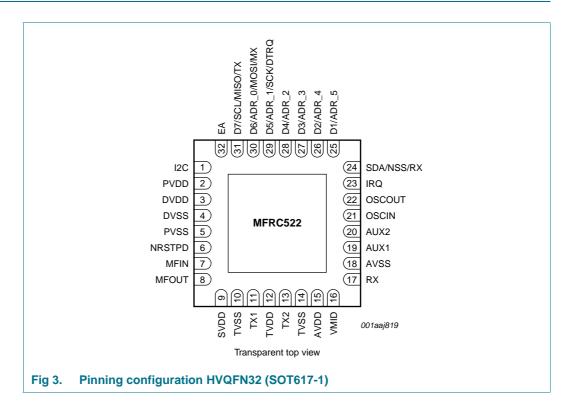

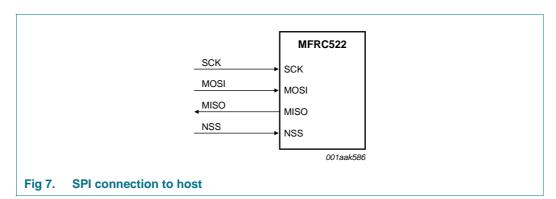

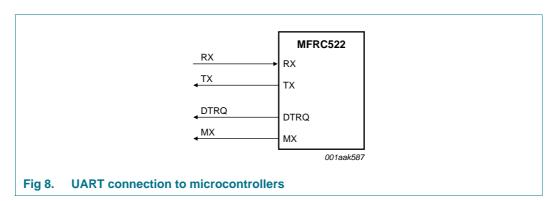

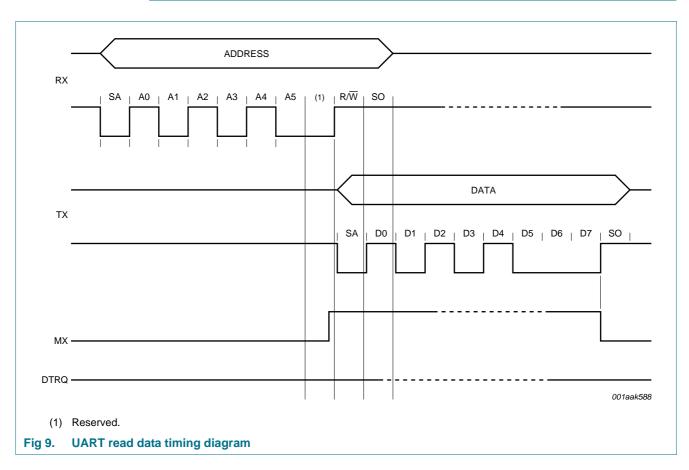

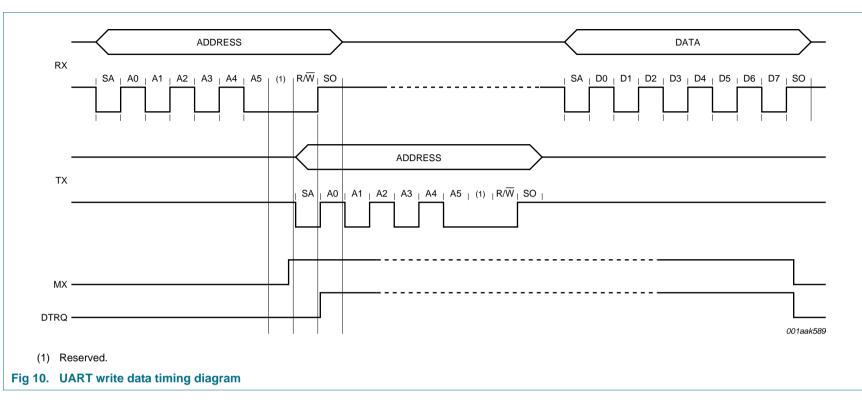

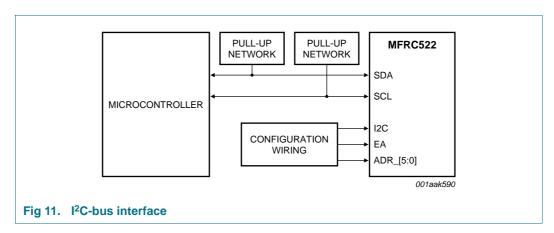

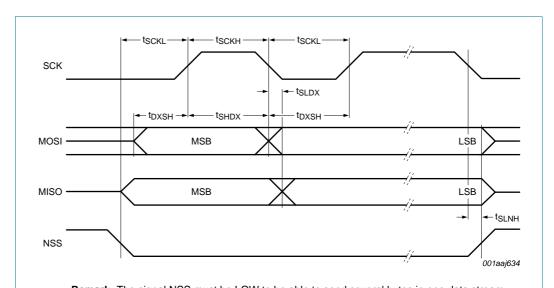

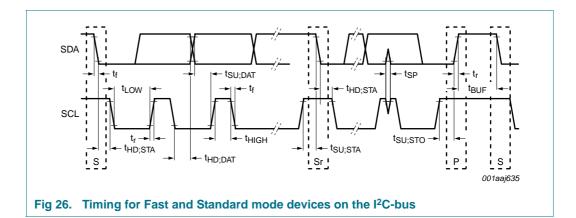

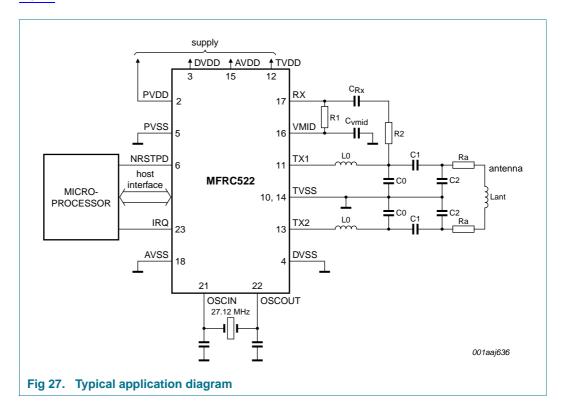

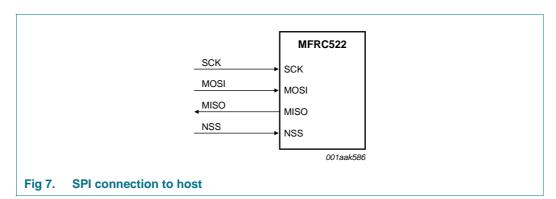

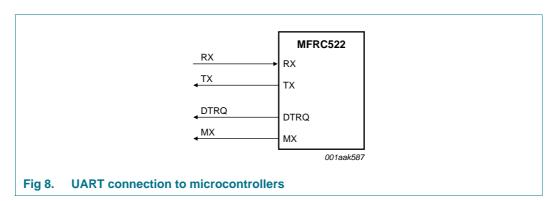

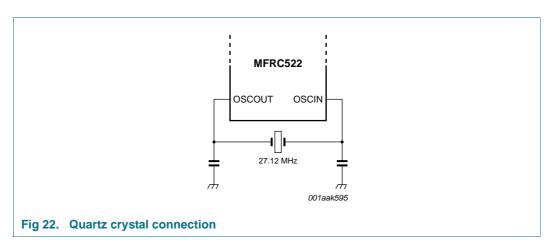

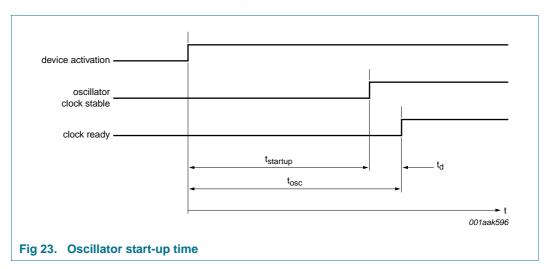

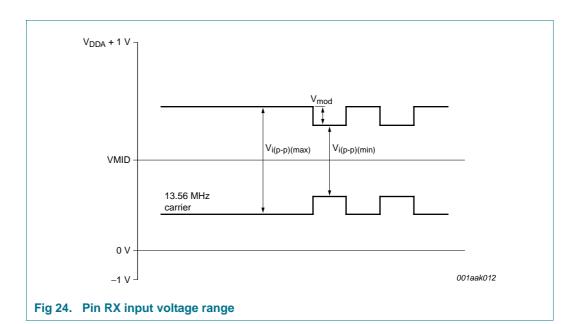

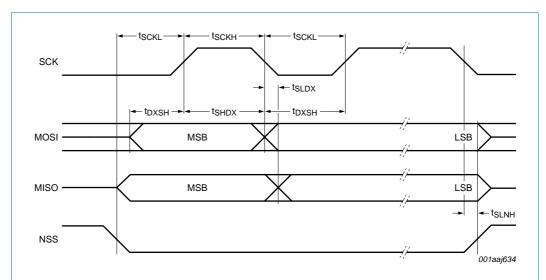

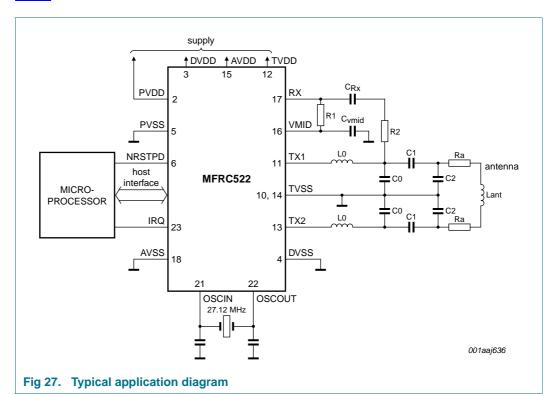

Εμείς θα κάνουμε χρήση αυτής της τεχνολογίας ως ακολούθως. Πάνω στο δικό μας RFID RC522 έχουμε 8 σημεία σύνδεσης. Αυτά είναι:

- ✓ **SDA** (Serial Data Signal),

- ✓ **SCK** (Serial Clock),

- ✓ **MOSI** (Master Out Slave In),

- ✓ MISO (Master In Slave Out),

- ✓ **IRQ** (Interrupt Request),

- ✓ **GND** (Ground Power),

- ✓ RST (Reset Circuit) και

- ✓ **3.3v** (3.3V Power In).

Θα πρέπει να συνδέσουμε όλους τους ακροδέκτες στο GPIO του Raspberry Pi εκτός από τη σύνδεση του **IRQ**. Η σύνδεση μπορεί να γίνει απευθείας καλωδιακά ή μέσα από συνδέσεις πάνω σε breadboard. Η διάταξη των ακροδεκτών είναι οφθαλμοφανές και δεν απαιτεί κάποιες άλλες επι πλέον συνδέσεις.

Σχήμα 23: Pin layout στο RFID-RC522

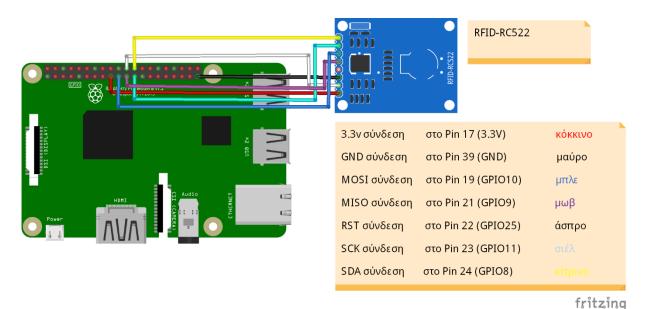

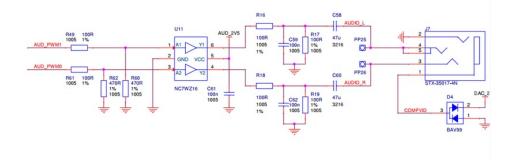

Στο παρακάτω σχήμα παραθέτουμε την κυκλωματική διασύνδεση με το Raspberry Pi μας.

Παρατηρούμε ότι έχουμε κάνει συνδέσεις σε ελεύθερες θέσεις στο GPIO μας, κάτι που θα μας βοηθήσει στο τέλος όταν ολοκληρώσουμε την διάταξη. Προς το παρόν οι τροφοδοσίες των 3.3V, 5V και GND είναι όλες ανεξάρτητα συνδεδεμένες, αλλά για λόγους ευκολίας μπορούμε στην ολική υλοποίηση να τις ομαδοποιήσουμε. Παραστατικά βλέπουμε και το παρακάτω σχέδιο με τις συνδέσεις στο Fritzing (**rfid-rc522 thesis.fzz**).

**Σχήμα 24**: Διασύνδεση του Raspberry Pi με το RFID-RC522

| ✓ | 3.3ν σύνδεση | στο <b>Pin 17 (3.3V</b> )  | κόκκιν |

|---|--------------|----------------------------|--------|

| ✓ | GND σύνδεση  | στο <b>Pin 39 (GND</b> )   | μαύρο  |

| ✓ | MOSI σύνδεση | στο Pin 19 (GPIO10)        | μπλε   |

| ✓ | MISO σύνδεση | στο Pin 21 (GPIO9)         | μωβ    |

| ✓ | RST σύνδεση  | στο Pin 22 (GPIO25)        | άσπρο  |

| ✓ | SCK σύνδεση  | στο <b>Pin 23</b> (GPIO11) | σιέλ   |

✓ SDA σύνδεση στο Pin 24 (GPIO8) κίτρινο✓ IRQ σύνδεση ασύνδετο

Έχοντας την διασύνδεση μας ένθεν και εκατέρωθεν μπορούμε να αναπτύξουμε των κώδικα σε python για την αναγνώριση.

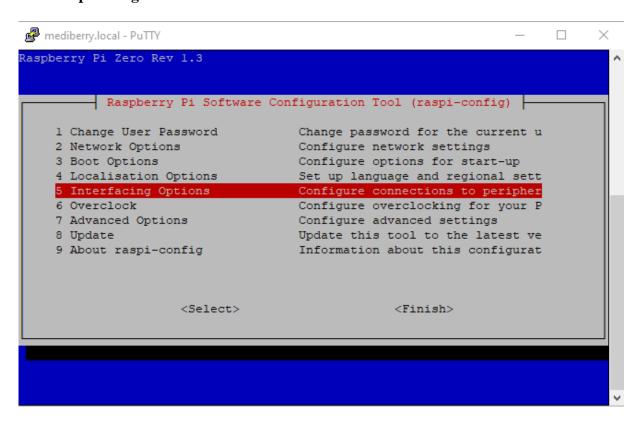

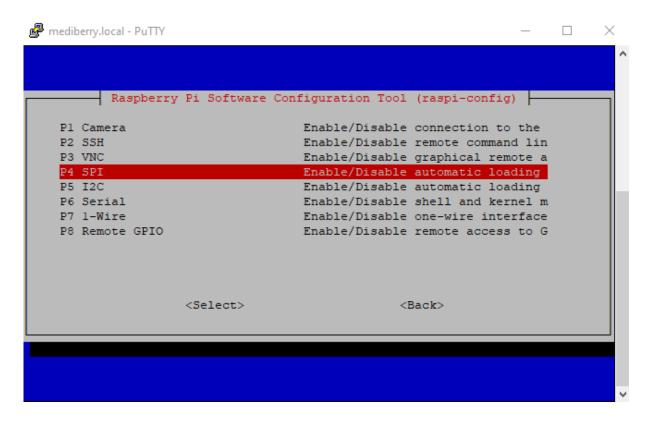

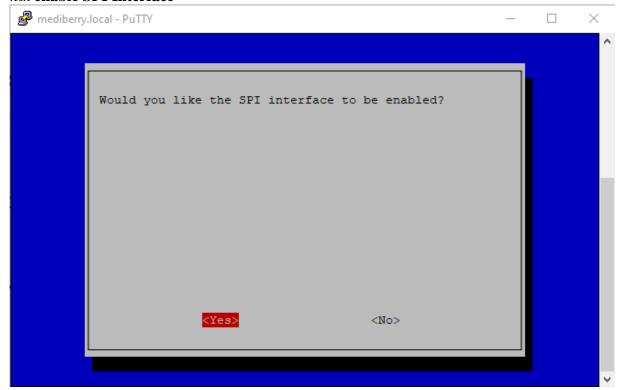

Τα προ απαιτούμενα είναι να έχουμε ενεργοποιήσει το SPI Interface στο Raspberry Pi από τις ρυθμίσεις του raspi-config.

### Sudo raspi-config

Μετά Interfacing Options

### και enable SPI Interface

Αφού ολοκληρωθεί η διαδικασία της ενεργοποίησης θα σώσουμε την κατάσταση και θα προβούμε σε επανεκκίνηση για να ενεργοποιηθεί πλήρως.

### Sudo reboot

Αφού γίνει αυτό θα πρέπει να ελέγξουμε αν έχει ενεργοποιηθεί το SPI Interface.

### lsmod | grep spi

```

mediberry.local-PuTTV

pi@mediberry:~$ lsmod | grep spi

spidev 7220 0

spi_bcm2835 7520 0

pi@mediberry:~$ [

```

Και βλέπουμε ότι είναι ενεργό το spi\_bcm2835 (Raspberry Pi).

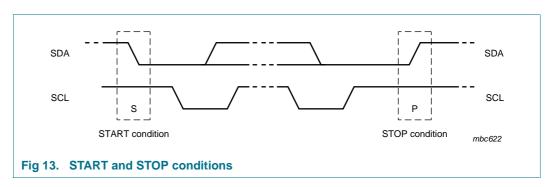

Στην δικιά μας υλοποίηση ζητούμενο είναι να τα εξής στάδια:

- 1) Αφού έχει έλθει σε ακινησία το τροχοφόρο όχημα ενεργοποιείτε ρουτίνα στον κώδικα του για να δουλέψει ο RFID αναγνώστης.

- 2) Ο RFID αναγνώστης είναι σε «**αναμονή**» για τυχόν σήμα από RFID πομπό τύπου κάρτας.

- 3) Αφού ταυτοποιηθεί ότι ανήκει σε «γνωστά» κλειδιά θα προχωρήσει ο κώδικας και θα τσεκάρει αν είναι στην σωστή θέση (π.χ. σταμάτησε το όχημα στη θέση 1 και είναι το RFID της θέσης 1 τότε προχωράει σαν αληθής η ρουτίνα, αλλιώς βγάζει λάθος).

- 4) Αν είναι στη σωστή θέση

- 5) Είναι και το αντίστοιχο κλειδί της θέσης;

- 6) Προχωράμε στον κώδικα δίνοντας εντολή στο αντίστοιχο πορτάκι (Θα εξηγήσουμε παρακάτω τι είναι το πορτάκι).

- 7) Εμφανίζουμε ενδεικτική λυχνία ότι είναι λάθος θέση ή κλειδί.

- 8) Αν δεν είναι το αντίστοιχο κλειδί της θέσης προχωράμε στον κώδικα και δίνουμε εντολή για συνέχιση της κίνησης του οχήματος.

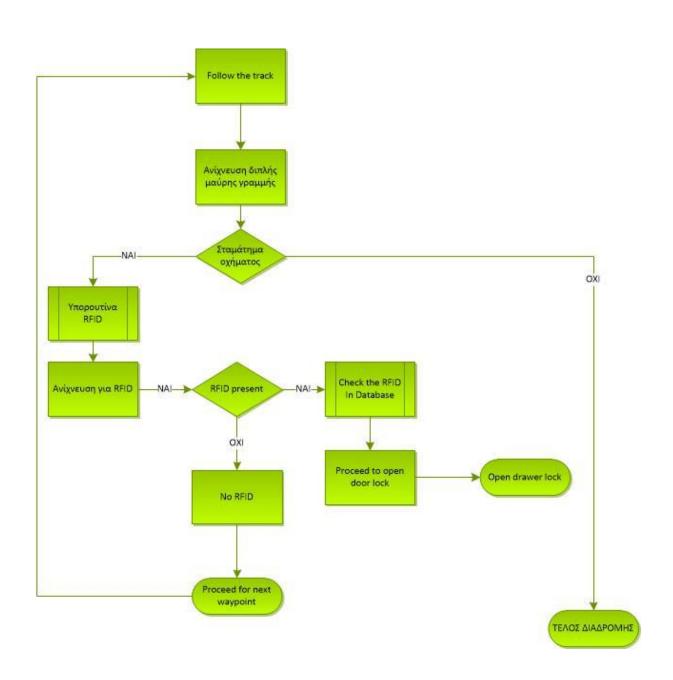

Μετά την λεκτική περιγραφή ακολουθεί ένα διάγραμμα ροής σε Microsoft Visio για την υλοποίηση του.

Προσοχή δίνει μόνο σημασία στο κομμάτι το πως δουλεύει η ανίχνευση του σήματος RFID και τι ρουτίνες δουλεύουν και τι στάδια υπάρχουν.

Το Πλήρες διάγραμμα ροής της όλης διάταξης θα αναλυθεί και θα παρουσιαστεί στο κεφάλαιο 7.

Μετά την λεκτική περιγραφή ακολουθεί το πρόγραμμα σε κώδικα python για την υλοποίηση του.

# Python script RFID

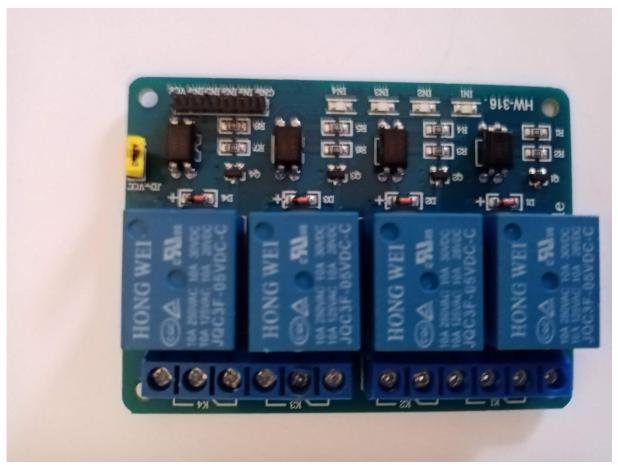

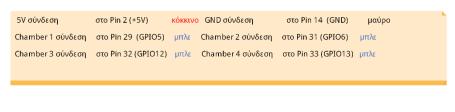

### 4.7 Relays

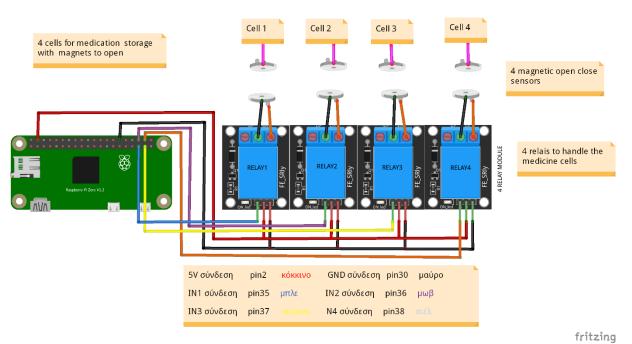

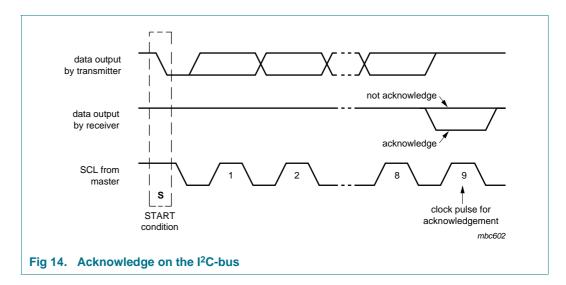

Το επόμενο στάδιο είναι το πως θα ανοίξουμε και θα κλείσουμε τα πορτάκια στα κελιά στο τροχοφόρο όχημα.

Για αυτό το σκοπό θα χρησιμοποιήσουμε ένα relay 4 καναλιών ειδικά σχεδιασμένο για Arduino/Raspberry τύπου HW-316 στα 5V για να κάνουμε την οδήγηση των επι μέρους κελιών φαρμάκων (medicine cell). Κάθε αριθμημένο κελί (από το 1 μέχρι το 4) περιέχει μέσα του το αντίστοιχο φάρμακο.

Στην προκειμένη περίπτωση πρέπει να είμαστε σε θέση να οδηγήσουμε κάθε κελί ξεχωριστά από την αντίστοιχη ρουτίνα του προγράμματος.

Σχήμα 25: Relay 4 καναλιών

### Η διαδικασία είναι η εξής:

Αφού γίνει η επιβεβαίωση από το RFid (δες πιο πάνω για την περιγραφή) τότε θα δοθεί από το πρόγραμμα η εντολή στα άκρα του Relays και συγκεκριμένα στις εισόδους IN1 έως IN4 ανάλογα με την περίπτωση για ενεργοποίηση εξόδου. Αυτό με τη σειρά του θα ενεργοποιήσει την αντίστοιχη έξοδο στο relays K1 έως K4. Οι έξοδοι των relays είναι συνδεδεμένα με μαγνητικούς αισθητήρες.

Παρακάτω βλέπουμε το σχηματικό σχεδιασμένο στο Fritzing (4 relais board thesis.fzz)

Σχήμα 26: Αποτύπωση σε Fritzing για τη χρήση 4 Relays

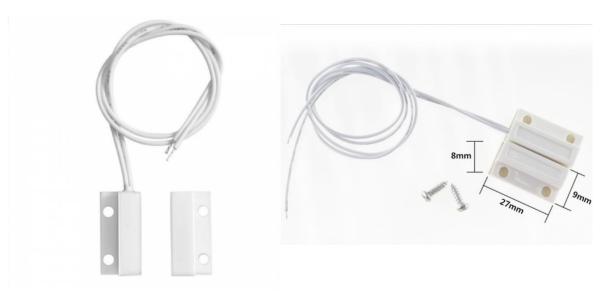

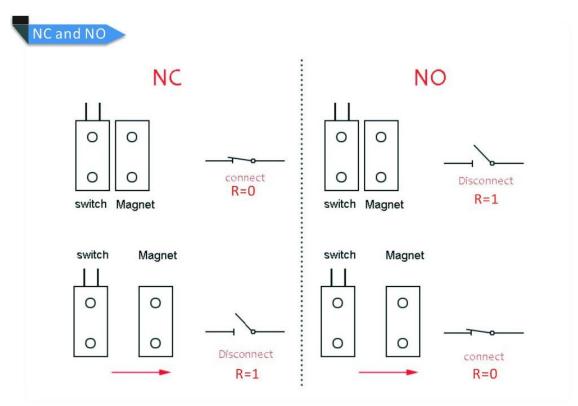

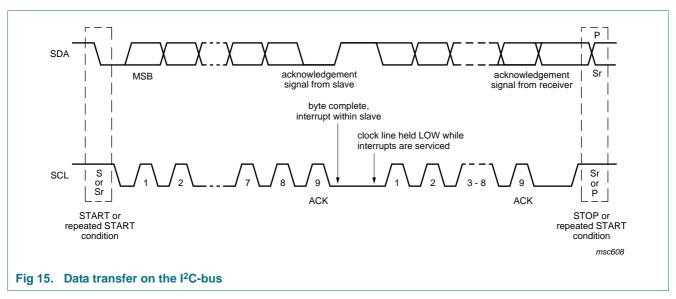

### 4.8 Μαγνητικός αισθητήρας

Το πως λειτουργεί κάθε μαγνητικός αισθητήρας ON/OFF θα γίνει περιγραφή πιο κάτω.

Ο μαγνητικός αισθητήρας ON/OFF που είναι ο ίδιος τύπος που έχουμε στους συναγερμούς στα παράθυρα θα είναι συνεχώς οπλισμένος δηλαδή ενεργοποιημένος (η εντολή έρχεται από τα Relay), ώστε να μην μπορεί να ανοίξει το κελί του φαρμάκου. Έτσι καταφέρνουμε να έχουμε την απαιτούμενη ασφάλεια και να μην μπορεί να ανοίξει το κελί από οποιονδήποτε άλλο.

Μόλις γίνει η επιβεβαίωση του ασθενούς ότι πρόκειται δηλαδή για την σωστή θέση και τον αντίστοιχο ασθενή τότε το relay δίνει εντολή αφόπλισης του μαγνητικού αισθητήρα και είναι πλέον δυνατόν να ανοίξει το κελί. Έτσι δεν διαρρέει ρεύμα στο εσωτερικό μέρος του μαγνητικού αισθητηρίου και απενεργοποιείτε η μαγνήτιση.

**Σχήμα 27**: Μαγνητικός αισθητήρας ΟΝ/ΟFF

Σχήμα 28: Παραστατικός τρόπος λειτουργίας του μαγνητικού αισθητήρα

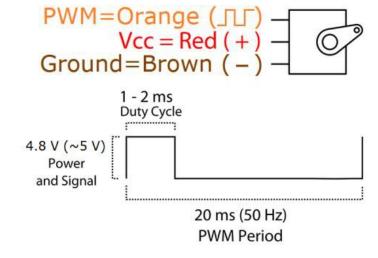

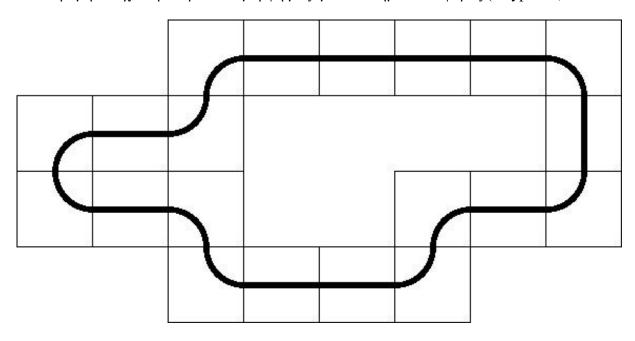

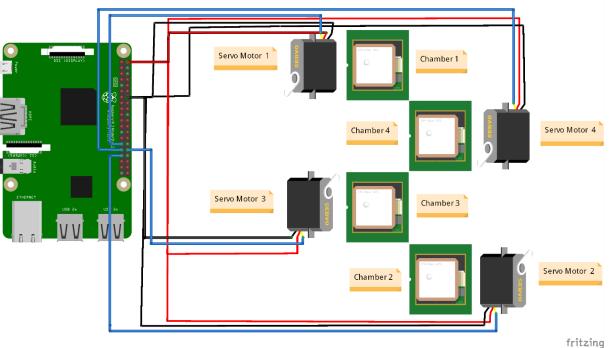

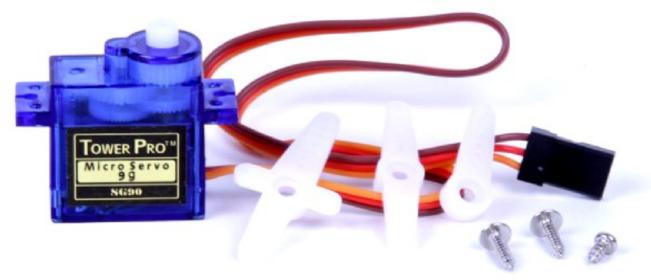

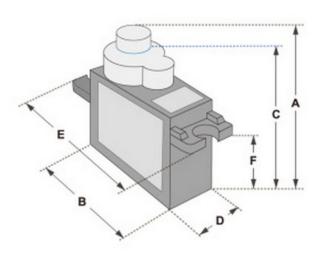

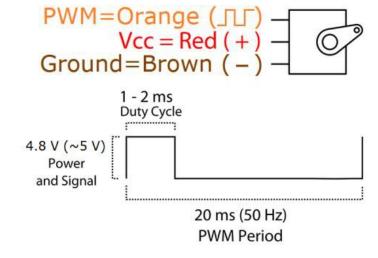

# 4.9 Servo κινητήρες

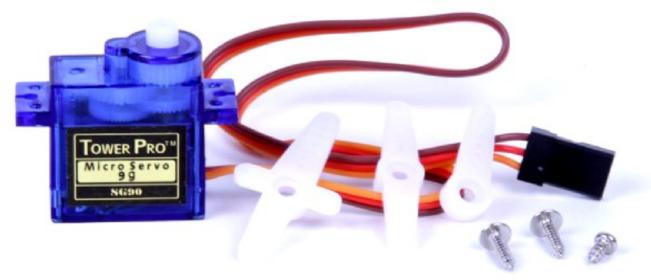

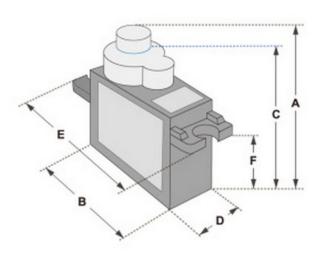

Οι Servo κινητήρες τύπου Tower Pro είναι βηματικοί κινητήρες με δυνατότητα περιστροφής του άξονα από 0° έως 360°. Είναι τριών ακροδεκτών με τροφοδοσία +5V, GND και πορτοκαλί την εντολή PWM ώστε να δίνει τον παλμό που θέλουμε.

Σχήμα 29: Micro Step motor τύπου Tower Pro και διάταξη ακροδεκτών

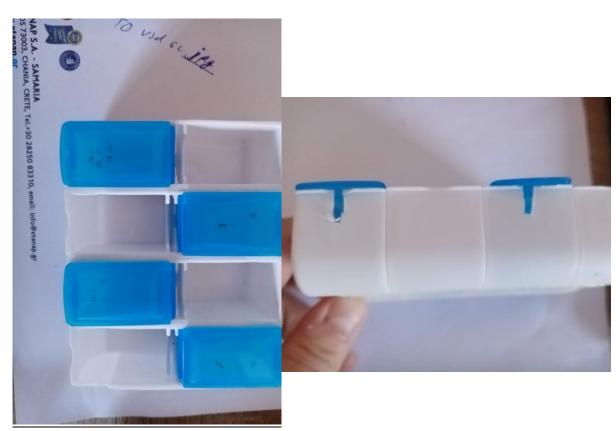

Σε αυτούς τους Servo κινητήρες έρχεται η εντολή από το πρόγραμμα να ανοιγοκλείσουνε κατά μια γωνία γύρω στις 90° ώστε να ανοίξει το καπάκι στο κελί (Chamber) και έτσι ο ασθενής να παραλάβει το φάρμακο του.

Μετά την περιστροφική κίνηση του ανοίγματος και το ξετάπωμα του κελιού ο άξονας περιστροφής θα κάνει την αντίστροφη κίνηση να επανέρθει στην αρχική του θέση αφού περάσουν κάποια λεπτά που εμείς θα ορίσουμε σαν κατώφλι μέσα στο πρόγραμμα. Όταν θα ολοκληρωθεί αυτή η επιστροφή του άξονα, ο ασθενής θα βεβαιωθεί οπτικά ότι επανήλθε στην θέση του και θα ταπώσει το κελί. Αυτό θα δώσει και το έναυσμα στον μαγνητικό αισθητήρα ON/OFF να οπλίσει και το τροχοφόρο να συνεχίσει την πορεία του. Παραστατικά το σχέδιο σε Fritzing (servo motor control.fzz)

Σχήμα 30: Αποτύπωση σε Fritzing για τη χρήση 4 Micro Server Motor

Στην τελική έκδοση βάζουμε και μια αντίσταση  $1~\rm K\Omega$  σε κάθε ακροδέκτη PWM για να μην έχουμε θέμα, σε κάθε μπλε αγωγό που φαίνεται στο σχήμα  $30~\rm k$ αι πριν πάει η γραμμή στο Raspberry.

Τεχνικά οι εγκοπές πάνω στο κουτί των φαρμάκων και ακριβέστερα στα πλάγια των κελιών είναι για να μπορέσουμε να περάσουμε τον άξονα του micro servo κινητήρα μέσα για να ανοιγοκλείσουμε το καπάκι. Επίσης στις παρακάτω εικόνες φαίνεται και η θέση των μαγνητικών αισθητηρίων πως έχουν τοποθετηθεί στο εσωτερικό και εξωτερικό περιμετρικά.

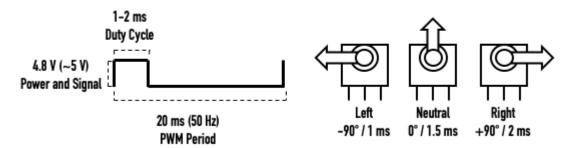

Για να υπολογιστεί το πόσο θα περιστρέφει ο άξονας του Step Motor θα πρέπει να υπολογίσουμε για 3 θέσεις το Duty Cycle και την αντίστοιχη γωνία περιστροφής. Θεωρούμε, ως αφετηρία την κεντρική  $(0^0)$  και θα περιστρεφόμαστε σε 2 θέσεις αριστερά  $90^0$  και δεξιά  $90^0$ . Στο παρακάτω σχήμα φαίνονται οι γωνίες περιστροφής για αριστερά κέντρο δεξιά.

#### LEARN ROBOTICS

Για να υπολογίσουμε τον κύκλο εργασίας επί της 100 για κάθε θέση θα πρέπει να κάνουμε διαίρεση της συνολικής περιόδου της πλήρης περιστροφής Next, convert the duty cycle times to percentages by dividing the position's duty cycle by the total PWM Period (20 ms). For example, the left position has a duty cycle = 1 ms. Therefore,  $1/20 \times 100\% = 5\%$ . I've included this handy chart for your reference.

# **Left Neutral Right**

| Angle (deg)     | -90  | 0      | +90  |

|-----------------|------|--------|------|

| Duty Cycle (ms) | 1 ms | 1.5 ms | 2 ms |

| Duty Cycle (%)  | 5%   | 7.5%   | 10%  |

Σχήμα 31: A) Pill box ευρείας χρήσης

**B)** Κάτοψη Pill box

Γ) Πλαΐνη όψη με εγκοπές χωρίς αισθητήρια

Σχήμα 32: Pill box με αισθητήρες μαγνητικούς και micro servo κινητήρα

### 5.1 Εισαγωγικά

Στο κεφάλαιο 5° θα δείξουμε λεπτομερώς βήμα προς βήμα το λογισμικό χρήσης για τη διασύνδεση του Raspberry Pi με τον Υπολογιστή για τον προγραμματισμό του καθώς και πως αναπτύχθηκε και υλοποιήθηκε όλο το λογισμικό μέχρι το τελικό στάδιο.

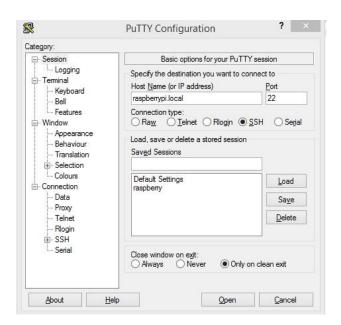

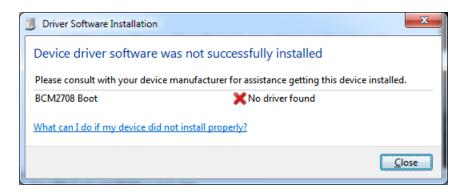

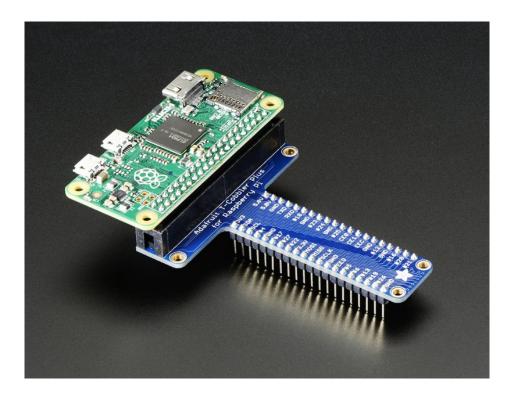

### 5.2 Βήματα για την διασύνδεση της μονάδας Raspberry Pi με τον Υπολογιστή

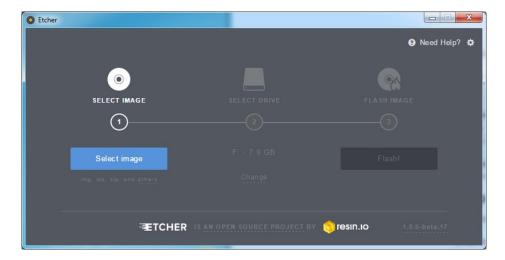

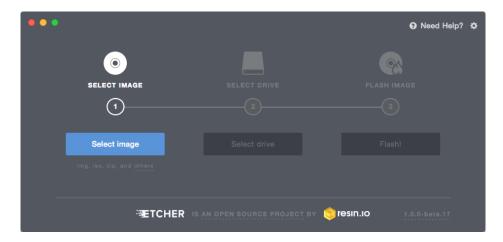

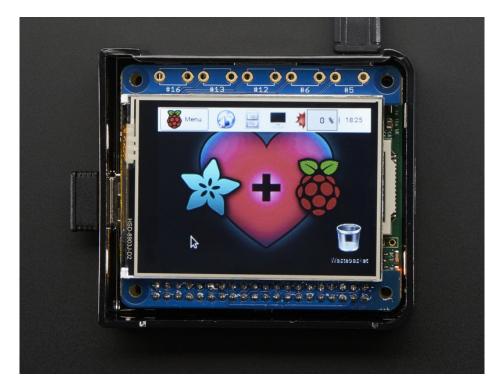

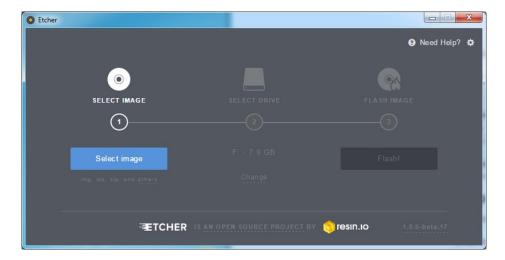

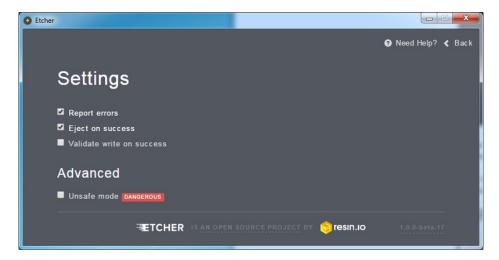

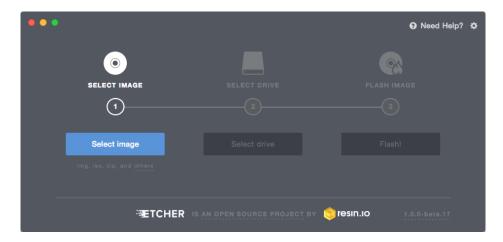

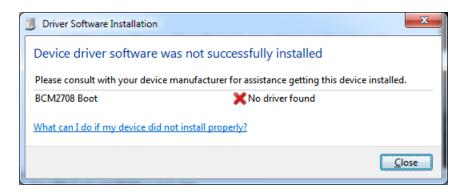

Ακολουθούν τα βήματα για την διασύνδεση της μονάδας **Raspberry Pi3**, **Pi Zero** ή **Pi Zero W** για να έχουμε SSH πρόσβαση μέσου της θύρας USB σε περιβάλλον Windows.

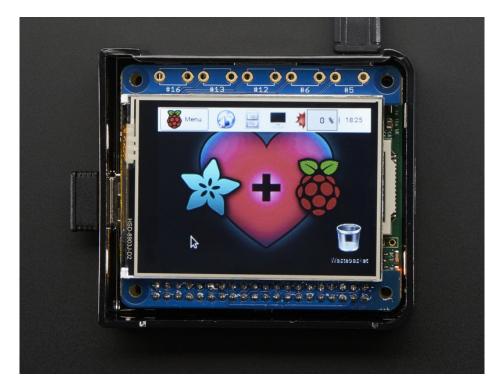

Μια από τις βασικότερες ερωτήσεις προκύπτει όταν έχουμε αγοράσει την μονάδα πως θα έχουμε πρόσβαση σε προγραμματιστικό περιβάλλον ή καλύτερα την διαχείριση χωρίς να χρειάζεται να συνδέσουμε επιπλέον εξοπλισμό όπως ένα USB Hub για την σύνδεση USB ποντίκι, USB πληκτρολόγιο ή και οθόνης για την αποτύπωση και λοιπών συσκευών όπως και σαφώς αντάπτορα για να συνδέσουμε από micro HDMI (που έχει το **Pi Zero**) σε HDMI για τη σύνδεση με οθόνη νέας τεχνολογίας ή ακόμα και σε τηλεόραση.

Όλα αυτά θα δούμε πως είναι περιττά και πως θα συνδέσουμε την μονάδα απλά μόνο με καλώδιο USB σε υπολογιστή / φορητό υλοποιώντας τα παρακάτω βήματα.

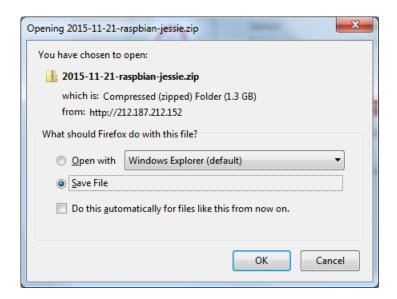

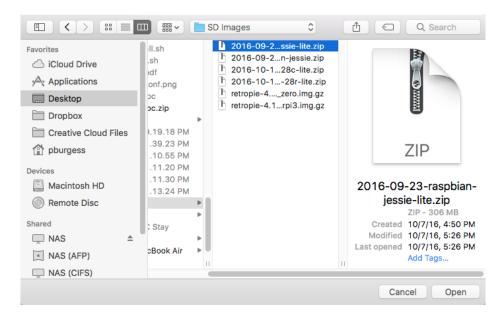

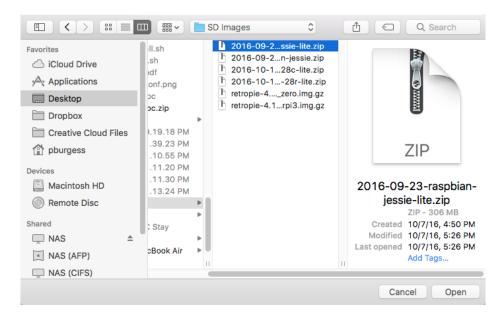

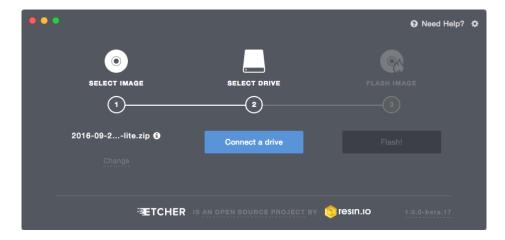

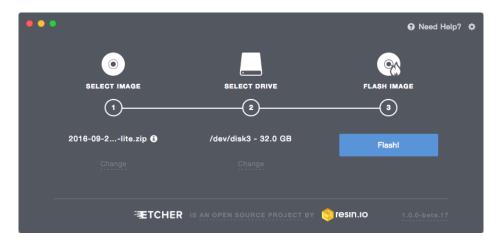

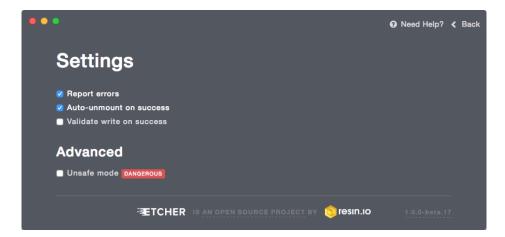

### Βήμα 10:

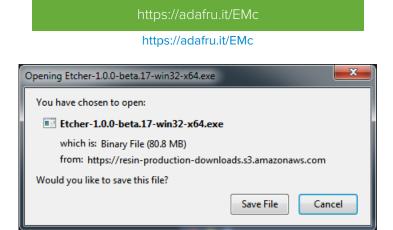

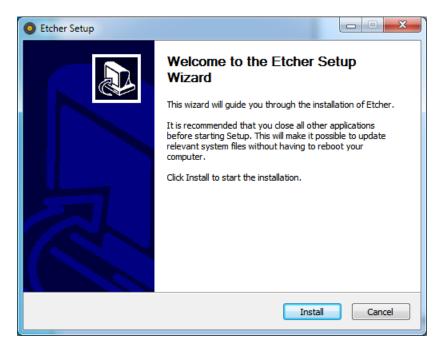

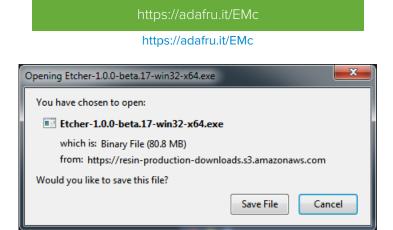

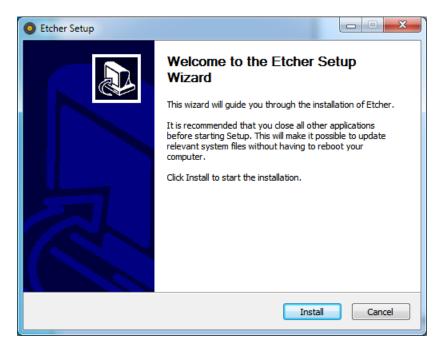

Κατεβάζουμε μια διανομή **Raspbian Stretch Lite** για το Raspberry Pi από την επίσημη ιστοσελίδα<sup>9</sup> (υπάρχουν τα images στις πηγές της Διπλωματικής).

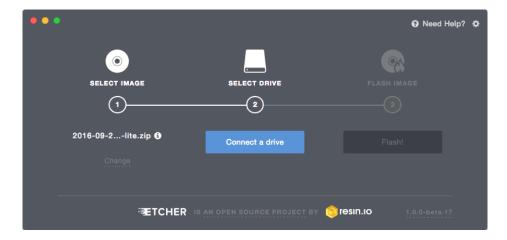

Την περνάμε με ένα πρόγραμμα εγγραφής $^{10}$  σε μια micro SD κάρτα χωρητικότητα τουλάχιστον 8GB.

# <u>Βήμα 2°:</u>

Το ssh πρωτόκολλο δεν είναι ενεργοποιημένο για λόγους ασφαλείας εξ αρχής στο λειτουργικό **Raspbian** και θα πρέπει χειροκίνητα να ενεργοποιηθεί εκ των υστέρων από το χρήστη πριν από την 1<sup>η</sup> χρήση. Για να το ενεργοποιήσουμε ακολουθούμε τα εξής βήματα:

- 1. Τρέχουμε το Σημειωματάριο.

- 2. Κάνουμε ένα κενό μέσα σε νέο έγγραφο.

- 3. Αποθηκεύουμε στο **root της SD κάρτας** ως νέο αρχείο με το όνομα **ssh και** κατάληξη «όλα τα αρχεία».

- 4. Κλείνουμε το αρχείο.

<sup>10</sup> Etcher πρόγραμμα εγγραφής εικόνων σε αποθηκευτικά μέσα.

<sup>&</sup>lt;sup>9</sup> <u>https://www.raspberrypi.org/downloads/ras</u>pbian/

### <u>Βήμα 3°:</u>

Επεξεργασία του αρχείου **config.txt** για να έχουμε πρόσβαση ssh προσθέτοντας στο τέλος του αρχείου το παρακάτω

### dtoverlay=dwc2

### **Βήμα 40:**

Επεξεργασία και αποθήκευση του αρχείου **cmdline.txt** για να έχουμε πρόσβαση **ssh** προσθέτοντας μετά το σημείο **rootwait** τα παρακάτω:

### modules-load=dwc2,g\_ether

Προσοχή να υπάρχει μονό κενό πριν και μετά το πρόσθετο στοιχείο γιατί αλλιώς δεν θα παίζει.

### **Βήμα 5°:**

Εγκατάσταση του **Bonjour** σε περιβάλλον Windows.

Για να έχουμε πρόσβαση **ssh** σε περιβάλλον Windows στο Raspberry Pi βάζοντας το με hostname ακολουθούμενο από .local (π.χ.: raspberrypi.local) θα πρέπει να εγκατασταθεί στο λειτουργικό μας η υπηρεσία Bonjour<sup>11</sup>.

#### Bήμα 6°:

Ενεργοποίηση του Pi Zero ή οποιουδήποτε Raspberry Pi

- 1. Βάζουμε την micro SD card μέσα στον ειδικό οδηγό στο Pi Zero.

- 2. Συνδέουμε το καλώδιο Micro-USB στην υποδοχή data/peripherals χωρίς να χρειαστεί να συνδέσουμε επιπλέον τροφοδοσία.

- 3. Δίνουμε τον απαιτούμενο χρόνο 2-3 λεπτών μέχρι που να φορτωθεί το λειτουργικό στο Pi Zero και να είναι έτοιμο προς χρήση.

#### <u>Βήμα 7°:</u>

Ανοίγουμε το πρόγραμμα **putty** για την επικοινωνία **ssh**.

Οι ρυθμίσεις είναι όπως φαίνονται στο παρακάτω σχήμα.

Στο περιβάλλον εκκίνησης μόλις ζητηθεί εισαγωγή στοιχείων βάζουμε:

- 1. Στο πλαίσιο Host Name (or IP address) το όνομα raspberrypi.local

- 2. Η πόρτα (**Port**) εξ' ορισμού είναι η **22** και η σύνδεση **Connection type** σετταρισμένη σε **SSH.**

<sup>11</sup> https://support.apple.com/kb/DL999?locale=en US

3. Πατάμε το **Open** και περιμένουμε να μας βγάλει στο πλαίσιο διαλόγου για τα διαπιστευτήρια στα οποία εισάγουμε:

Username: **pi** και password: **raspberry**.

Μετά την επιτυχή είσοδο θα πρέπει να είμαστε στο root του Raspberry Pi.

Σχήμα 33: Ρυθμίσεις για πρόσβαση ssh

# <u>Βήμα 8°:</u>

Πρόσβαση στο δίκτυο από το σύστημα των Windows

Επειδή εξ' αρχής η σύνδεση η ενσύρματη στο σύστημα των Windows δεν είναι ρυθμισμένη να παρέχει και ταυτόχρονα διασύνδεση στο Internet, θα πρέπει από μεριάς μας να πραγματοποιήσουμε κάποιες χειροκίνητες ενέργειες ώστε να δώσουμε στην μονάδα πλήρη πρόσβαση.

Αυτά τα βήματα περιγράφονται στη συνέχεια.

- 1. Ανοίγουμε τον **Πίνακα Ελέγχου και τρέχουμε το Κέντρο Δικτύου και κοινής Χρήσης.**

- 2. Εξαρτάται από το τρόπο με τον οποίο είμαστε συνδεδεμένοι για να επιλέξουμε ή την ενσύρματη ή την ασύρματη σύνδεση μας και μετά

- 3. Click **Ιδιότητες**

- 4. Click στην καρτέλα κοινή χρήση.

- 5. Ενεργοποιούμε την επιλογή Να επιτρέπετε η χρήση άλλων χρηστών του διαδικτύου από αυτή τη σύνδεση.

- 6. Click **ΟΚ** και μετά **Κλείσιμο**.

- 7. Για έλεγχο θα μπορούσα μέσα στο παράθυρο να βάζαμε ping <u>www.hmu.gr</u> και να δούμε εάν έχουμε απάντηση στα αιτήματα ping.

Ολοκληρώνοντας αυτά τα βήματα θα έχουμε πετύχει την διασύνδεση της μονάδας Raspberry με τον Η/Υ ή και φορητό μας.

### Προσοχή!!!

Πρέπει οπωσδήποτε να εκτελεστούν τα βήματα πάντα πριν την πρώτη χρήση και σύνδεση της πλακέτας ανεξαρτήτως μηχανήματος.

# 5.3 <u>Βήματα για την αυτοματοποιημένη εκκίνηση της μονάδας Raspberry Pi για</u> την εκτέλεση του προγράμματος

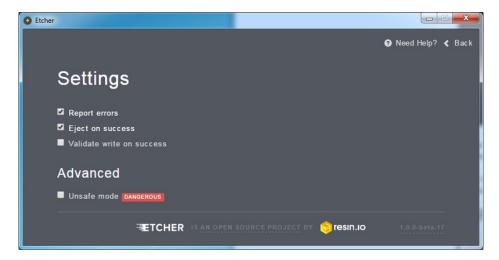

Ένα άλλο ζήτημα είναι πως θα κάνουμε το Raspberry Pi να τρέξει αυτοματοποιημένα με την εκκίνηση το πρόγραμμα που θέλουμε.

Το Raspberry δεν διαθέτει autorun όπως διαθέτει το Arduino με αποτέλεσμα να έχουμε πρόβλημα για την αυτόματη εκτέλεση προγράμματος κάθε φορά που αυτό ενεργοποιείτε ή που τίθεται σε λειτουργία μετά από εκκίνηση.

Με το **Cron** που υπάρχει στα συστήματα Linux, μπορούμε να κάνουμε προγραμματισμό πότε θέλουμε να επαναληφθούν κάποιες εργασίες στο χώρο-χρόνο δίνοντας στον προγραμματιστή άπειρες δυνατότητες. Εμείς θα προσπαθήσουμε να το προσαρμόσουμε στα μέτρα μας τρέχοντας ένα script σε python που θα τρέχει το πρόγραμμα μας κάθε φορά που εκκινείτε το Raspberry Pi.

### <u>Βήμα 1°:</u> Δημιουργία του Python Script

Το πρώτο βήμα είναι να δημιουργήσουμε το script σε Python. Αυτό θα τρέχει όταν θα κάνει boot. Είναι πολύ σημαντικό να γνωρίζουμε το ακριβές όνομα και τη θέση που βρίσκετε. Στη δικιά μας υλοποίηση θα το ονομάσουμε «Mediberry.py» και θα το αποθηκεύσουμε στην τοποθεσία «/home/pi/».

Βλέπουμε και τσεκάρουμε αν έχουμε δώσει τη σωστή θέση στο αρχείο

#### cat /home/pi/Mediberry.py

Θα πρέπει να μας δείξει το περιεγόμενο του script που φτιάξαμε.

Εδώ σημειώνουμε ότι θα πρέπει να έχουμε διαπιστώσει ότι το συντάξαμε σωστά γιατί τρέχει κατά την εκκίνηση και δεν είναι εύκολο να το διορθώσουμε άπαξ και τρέξει.

### Βήμα 2°: Δημιουργία νέου Cron job

Για τη δημιουργία ενός νέου **Cron job** θα πρέπει να αλλάξουμε το «**crontab**». Είναι στην ουσία ένας πίνακας με λίστα από αυτοματοποιημένες εργασίες που ο **Cron** εποπτεύει και εκτελεί βάσει χρονοδιαγράμματος. Για να το τροποποιήσουμε θα εκτελέσουμε τις εξής εντολές:

#### sudo crontab -e

Κάθε χρήστης του λειτουργικού συστήματος έχει το δικό του Crontab, οπότε για να αποφύγουμε τυχόν δυσλειτουργίες που μεταφράζετε να αστοχεί να τρέχει το προαναφερθέν script από όλους τους χρήστες, στόχος μας είναι να το περάσουμε ως διαχειριστής admin οπότε γι' αυτό βάζουμε ως πρόθεμα το «sudo» στο «crontab -e». Οπότε θα πάρουμε ως αποτέλεσμα αυτό που βλέπουμε στην παρακάτω εικόνα.

**Σχήμα 34**: Αρχική οθόνη στο Crontab

Στο τέλος αυτού θα πρέπει να περάσουμε το εξής για να τρέχει κατά την εκκίνηση το script

#### @reboot sudo python Mediberry.py &

Το Cron τώρα μαθαίνει ότι σε κάθε εκκίνηση boot (or reboot or start-up) θέλουμε να τρέξουμε το **Mediberry.py αυτόματα στην Python. Το «και» στο τέλος «&»** έχει την έννοια να τρέχει στο παρασκήνιο και δε σταματάει όπως πριν.

Στην οθόνη θα βλέπουμε τα εξής:

Σχήμα 35: Οθόνη στο Crontab μετά την εισαγωγή του script μας

Για να το σώσουμε πατάμε «CTRL-X» για έξοδος, μετά «Υ» για επιβεβαίωση και στο τέλος «Return». Μετά από αυτή τη διαδικασία επιστρέφουμε στο Command Prompt και κάνουνε τα τεστ μας στην επόμενη επανεκκίνηση.

#### Sudo reboot

Αφού το έχουμε τώρα σεττάρει κάθε φορά θα τρέχει με την εκκίνηση του Pi.

Θα υπάρξουν όμως και φορές που δεν θα θέλουμε να τρέχει αυτόματα το σκριπτάκι και για αυτό το λόγο θα πρέπει να το σταματήσουμε.

Στόχος είναι πληκτρολογώντας την παρακάτω εντολή να βρούμε τον αριθμό εκτέλεσης της διαδικασίας και να του κάνουμε «kill».

#### Ps aux | grep /home/pi/Mediberry.py

Μέσα στα όλα αποτελέσματα μας βγάζει και τα παρακάτω από όπου και σταματάμε την εκτέλεση δίνοντας του την τελική εντολή «kill» με δικαιώματα διαχειριστή.

root 1863 0.0 1.0 24908 4012 ? SI 19:45 0:00 python /home/pi/Mediberry.py

#### sudo kill 1863

Στη δικιά μας περίπτωση για την εκτέλεση του προγράμματος θα ενεργήσουμε απλούστατα καλώντας το αντίστοιχο αρχείο Mediberry.py οπότε η εντολή στην κονσόλα θα είναι:

#### python Mediberry.py

και η εκτέλεση του προγράμματος θα μας βγάλει το welcome screen.

```

raspberrypi.local - PuTTY

pi@raspberrypi:~$ python Mediberry.py

***********************

*********************

Hellenic Mediterranean

University HMU

Master Thesis

Master Course TeleAuto

Title : Mediberry

Author Zervoudakis Antonios ####

#### Copyright (c)2020

####

#### Email: mtt9@edu.hmu.gr

####

#### Email: zervoud@hmu.gr

####

************************

**********************

### Welcome to the Presentation of ###

Master Thesis MEDIBERRY

***********************

pi@raspberrypi:~$

```

Σχήμα 36: Αρχική οθόνη εκτέλεσης

Στη συνέχεια στο κεφάλαιο 6 παραθέτουμε το πρόγραμμα της υλοποίησης

# Κεφάλαιο 6°

### 6.1 Εισαγωγικά

Εν συνεχεία, στο κεφάλαιο **6**° ακολουθώντας όλα τα στάδια που προαναφέρθηκαν θα παρουσιαστούν όλα τα στάδια υλοποίησης μαζί αφού έχουν διεξοδικά επιτυχώς αναλυθεί και από το εργαστηριακό κομμάτι προχωράμε στην αυτού καθαυτού υλοποίηση και στα σενάρια υλοποίησης σε πραγματικό περιβάλλον.

Τρία Σενάρια θα μας απασχολήσουν σε αυτή την υλοποίηση

- 1. Υλοποίηση σε πλήρη λειτουργία

- 2. Υλοποίηση με RFID σε λάθος θέσεις

- 3. Υλοποίηση με εμπόδιο στην διαδρομή

Πρώτα από όλα όμως θα δώσουμε το πλήρες διάγραμμα ροής της υλοποίησης.

### 6.2 Διάγραμμα ροής της υλοποίησης

Το πλήρες διάγραμμα ροής της υλοποίησης σας μας φαίνεται στο παρακάτω σχήμα

Σχήμα 37: Πλήρες διάγραμμα ροής "Mediberry"

### 6.3 Το πλήρες σχέδιο σε Fritzing