## Design and Implementation of an Memory Management Unit (MMU)

School of Engineering - Department of Informatics Engineering

T.E.I. Crete

by George Timbakianakis R.N.:2805

$1 \ 10 \ 2015$

## Abstract

As the modern world processes larger amounts of data and demand increases for massive amounts of memory, the need of efficient memory management also becomes critical. The aim of this study is to develop and implement a memory management unit (MMU) utilising the AXI interface protocol in order to create an ip module capable of obeying the basic rules of memory management through address translation. The MMU module will be implemented on a ZedBoard<sup>TM</sup> development platform using the Xilinx Zynq $(\mathbb{R})$ -7000 All Programmable SoC. At the end of this study we ended up with an versatile MMU module that conforms with the AXI4 interface protocol that can translate given addresses from the Zynq $(\mathbb{R})$ -7000 core and can perform memory writes to the translated addresses. The IP is fully designed, from the top up, with versatility in mind, enabling it to be used in a variety of situations as well as an educational tool for future student engineers.

Thesis Supervisor: Kornaros George Title: Professor, Dept. of Informatics Engineering

## Acknowledgements

There are many people who deserve recognition and thanks for contributing to the completion of this thesis project.

My parents, Demetres and Athena Timbakianakis, who have always supported my aspirations and endeavours in life.

My fellow student, Spyros Chiotakis for providing much-needed advice during my research.

Professor George Kornaros, for giving me the opportunity to participate in the ISCA lab facilitating the entire process from beginning to end. Finally, a huge thank you to Professor Fragopoulou Paraskevi that gave me the means and inspiration I needed.

## Contents

| 1        | Intr              | oduction 1                                                                                                                          |

|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1               | Memmory Managment Units                                                                                                             |

|          | 1.2               | Overview of FPGAs 22                                                                                                                |

|          | 1.3               | Purpose                                                                                                                             |

| <b>2</b> | Тоо               | ls                                                                                                                                  |

| -        | 2.1               | Hardware                                                                                                                            |

|          | 2.2               | Software                                                                                                                            |

|          | 2.3               | Used Languages                                                                                                                      |

|          | 2.0               | 2.3.1 VHDL                                                                                                                          |

|          |                   | 2.3.2 TCL                                                                                                                           |

| 0        | Ŧ                 |                                                                                                                                     |

| 3        | <b>Imp</b><br>3.1 | lementation 7<br>RAM                                                                                                                |

|          | 3.2               | MMU Top Level                                                                                                                       |

|          | 3.3               | AXI Interface                                                                                                                       |

|          | 0.0               | 3.3.1 Slave AXI Interface                                                                                                           |

|          |                   | 3.3.2 Master AXI Interface                                                                                                          |

|          |                   | 3.3.3 Complete IP                                                                                                                   |

|          |                   | 3.3.4 IP Modes                                                                                                                      |

|          | 3.4               | Design                                                                                                                              |

|          | -                 | 3.4.1 PS                                                                                                                            |

|          |                   | 3.4.2 Targets                                                                                                                       |

|          |                   | 3.4.3 AXI Interconnects                                                                                                             |

|          |                   | 3.4.4 Complete Design $\ldots \ldots 19$ |

| 4        | Test              | 20                                                                                                                                  |

| Т        | 4.1               | Ram Testing                                                                                                                         |

|          | 1.1               | 4.1.1 TestBench                                                                                                                     |

|          |                   | 4.1.2 Results                                                                                                                       |

|          | 4.2               | Top Level Testing   23                                                                                                              |

|          |                   | 4.2.1 TestBench                                                                                                                     |

|          |                   | 4.2.2 Results                                                                                                                       |

|          | 4.3               | IP Testing                                                                                                                          |

|          |                   | 4.3.1 Testing Methodology                                                                                                           |

| <b>5</b> | Con               | clusions 30                                                                                                                         |

| -        | 5.1               | Future Work   30                                                                                                                    |

|          |                   |                                                                                                                                     |

| Α | Abbreviations | 31 |

|---|---------------|----|

| В | .tcl Scripts  | 33 |

|   | B.1 test.tcl  | 33 |

|   | B.2 call.tcl  | 34 |

|   | B.3 store.tcl | 34 |

# List of Figures

| $1.1 \\ 1.2 \\ 1.3$ | Compute System with MMU1Generic FPGA Architecture2Switch block pins with different switch flexibility.3 |

|---------------------|---------------------------------------------------------------------------------------------------------|

| $2.1 \\ 2.2$        | $ZedBoard^{TM}$                                                                                         |

| 3.1                 | Abstract MMU Design    7      Ram Store Procedure    9                                                  |

| $3.2 \\ 3.3$        |                                                                                                         |

| э.э<br>3.4          | Ram Read Procedure    9      AXI4 Interface Design    10                                                |

| $3.4 \\ 3.5$        | Packaged MMU IP Block                                                                                   |

| 3.6                 | Store Mode FSM                                                                                          |

| 3.7                 | Translation Mode FSM   15                                                                               |

| 3.8                 | Zynq Processing System                                                                                  |

| 3.9                 | Targets                                                                                                 |

| 3.10                | AXI BRAM Controller                                                                                     |

| 3.11                | Interconnect                                                                                            |

| 3.12                | Complete Design                                                                                         |

| 4.1                 | RAM Write Simulation                                                                                    |

| 4.2                 | RAM Read Simulation                                                                                     |

| 4.3                 | RAM Write Fail                                                                                          |

| 4.4                 | Top Level Storing                                                                                       |

| 4.5                 | Top Level Translating                                                                                   |

| 4.6                 | Synthesized Design with ILA core                                                                        |

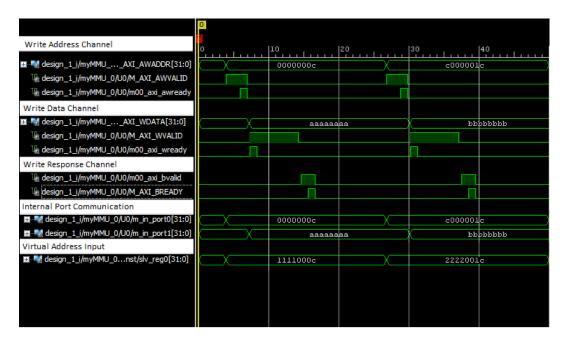

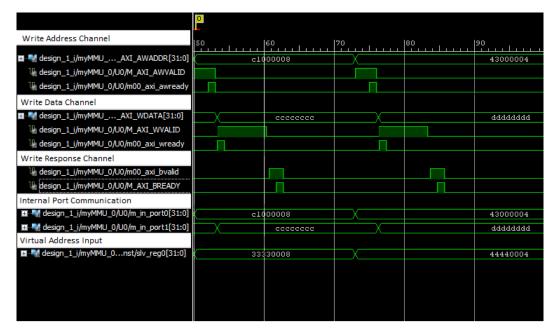

| 4.7                 | ILA Monitoring of Writes A                                                                              |

| 4.8                 | ILA Monitoring of Writes B                                                                              |

## List of Tables

| 3.1 | MMU Slave Registers           | 11 |

|-----|-------------------------------|----|

| 4.1 | MMU AXI Signals               | 26 |

| 4.2 | Testing Translations          | 27 |

| 4.3 | Testing Stored Data Addresses | 27 |

## Chapter 1

## Introduction

### 1.1 Memmory Managment Units

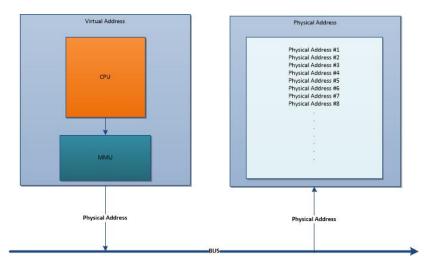

A memory management unit (MMU), sometimes called paged memory management unit (PMMU), is a computer hardware unit having all memory references passed through itself, primarily performing the translation of virtual memory addresses to physical addresses. It is usually implemented as part of the central processing unit (CPU), but it also can be in the form of a separate integrated circuit. An MMU effectively performs virtual memory management, handling at the same time memory protection, cache control, bus arbitration and, in simpler computer architectures (especially 8-bit systems), bank switching.

Modern MMUs typically divide the virtual address space (the range of addresses used by the processor) into pages, each having a size which is a power of 2, usually a few kilobytes, but they may be much larger. The bottom bits of the address (the offset within a page) are left unchanged. The upper address bits are the virtual page numbers.

Figure 1.1: Compute System with MMU

## 1.2 Overview of FPGAs

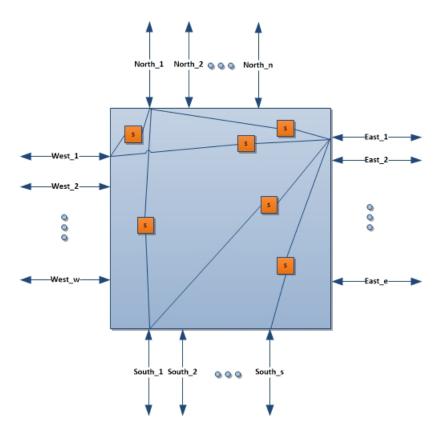

Field Programmable Gate Arrays (FPGAs) are used for rapid prototyping of digital circuits. The design and test of digital systems are very time-efficient and cost-efficient with FPGAs. They are composed of programmable digital blocks and programmable interconnect. Figure 1.1 shows a typical architecture of an FPGA. Programmable Logic Blocks (PLBs) represent the programmable digital block. A cluster of PLBs is called a Configurable Logic Block (CLB). Switch Blocks (SB) represent the programmable interconnect. PLBs may be connected directly to a switch block (like the one in Figure 1-1) or to interconnect. PLBs can implement small digital circuits and programmable interconnect can connect the small digital blocks to constitute a complex digital system. If there are enough PLBs and interconnect resources, most digital circuits can be implemented on FPGAs.

Figure 1.2: Generic FPGA Architecture

Since the switches in switch blocks consume more area and have a larger capacitance than wires in Application Specific Integrated Circuits (ASIC), FPGAs are typically 10 times larger and 3 times slower than ASICs. The higher capacitance also results higher power consumption even at equal speed. To make FPGAs suitable for more applications, their speed and power consumption should be improved.

Figure 1.3: Switch block pins with different switch flexibility.

In switch blocks, the number of possible connections between one pin to other pins is called the flexibility of the pin. For example, in Figure 1-2, the switch flexibility of South\_ W is 1, the flexibility of West\_ 1 and South\_ 1 is 2, the flexibility of North\_ 1 is 3, and the flexibility of East\_ 1 is 4. The pins that are not connected to anywhere have a flexibility of 0. Switch flexibility of 3 or 4 is suggested to be very optimum if all pins have the same flexibility.

## 1.3 Purpose

The purpose of this Thesis is to implement a MMU for use in Zynq-7000 SoC designs. The main reason for implementing this type of MMU is to be able to perform memory address translations without intervention from the processor.

There are some specific features that should be supported by the MMU. It must be connected to a AXI4 Master port of the Zynq PS and it must be able to write to multiple AXI4 Slave ports. It must also be able to be configured through its Slave port by the Zynq PS.

When implemented its functions must be tested and verified.

## Chapter 2

## Tools

## 2.1 Hardware

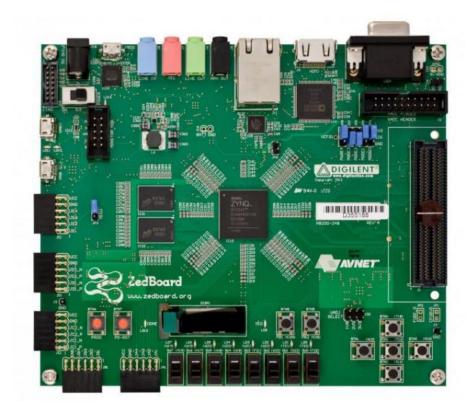

#### $\mathbf{ZedBoard}^{\mathsf{TM}}$

ZedBoard<sup>TM</sup> is a complete development kit for designers interested in exploring designs using the Xilinx Zynq®-7000 All Programmable SoC. The board contains all the necessary interfaces and supporting functions to enable a wide range of applications. The expandability features of the board make it ideal for rapid prototyping and proof-of-concept development.

Figure 2.1: ZedBoard<sup>TM</sup>

## 2.2 Software

#### Vivado®

The Vivado® Design Suite delivers a SoC-strength, IP-centric and systemcentric, next generation development environment that has been built from the ground up to address the productivity bottlenecks in system-level integration and implementation. The Vivado Design suite is a Generation Ahead in overall productivity, ease-of-use, and system level integration capabilities.

Figure 2.2: Vivado Logo

#### SDK

The Software Development Kit (SDK) is the Xilinx Integrated Design Environment for creating embedded applications on any of Xilinx' award winning microprocessors for  $Zynq(\mathbb{R})$ -7000 All Programmable SoCs, and the industry-leading MicroBlaze<sup>TM</sup>. The SDK is the first application IDE to deliver true homogenous and heterogeneous multi-processor design and debug.

#### AMBA AXI Interface

AXI is part of ARM AMBA, a family of micro controller buses first introduced in 1996. The first version of AXI was first included in AMBA 3.0, released in 2003. AMBA 4.0, released in 2010, includes the second major version of AXI, AXI4. There are three types of AXI4 interfaces:

- AXI4: For high-performance memory-mapped requirements.

- AXI4-Lite: For simple, low-throughput memory-mapped communication.

- AXI4-Stream: For high-speed streaming data.

In this MMU implementation, AXI4-Lite will be the interface of choice due to the fact that high throughput is not needed as well as the burst function is unnecessary.

## 2.3 Used Languages

In this Thesis programming languages were used to describe the hardware components as well as providing testing algorithms.

### 2.3.1 VHDL

VHDL (VHSIC Hardware Description Language) is a hardware description language used in electronic design automation to describe digital and mixed-signal systems such as field-programmable gate arrays and integrated circuits. VHDL can also be used as a general purpose parallel programming language.

in this project VHDL is used to describe the hardware components of the design tat will, later, be synthesized and implemented.

### 2.3.2 TCL

Tcl (originally from Tool Command Language, but conventionally spelled "Tcl" rather than "TCL"; pronounced as "tickle" or "tee-see-ell") is a scripting language created by John Ousterhout. Originally "born out of frustration", according to the author, with programmers devising their own languages intended to be embedded into applications, Tcl gained acceptance on its own.

It is commonly used for rapid prototyping, scripted applications, GUIs and testing. Tcl is used on embedded systems platforms, both in its full form and in several other small-footprint versions.

In this project TCL is used for scripting purposes.

## Chapter 3

## Implementation

This chapter describes how the MMU IP was implemented. It contains information about the structure of the IP and the implemented code. It also describes how the AXI4 Lite interfaces are implemented and how the finished module was incorporated in a final design. Explanations of the two FSM:s that provides the functionality of the MMU IP are included. A description of a test transaction is provided.

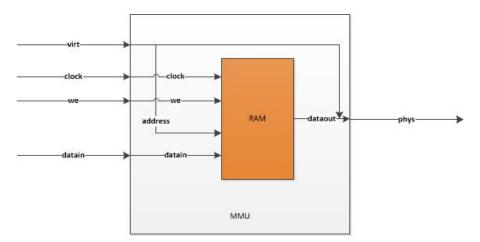

### 3.1 RAM

At the heart of the MMU is a rather simple design. As a lookup table, there is a 16 bit Random Access Memory design and all the routing and manipulating of the address is done with simple logic.

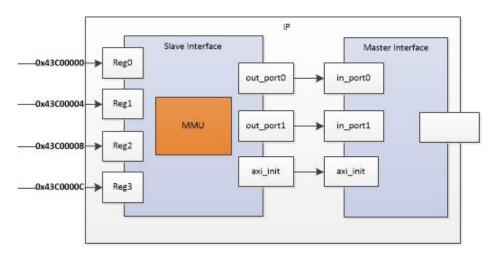

Figure 3.1: Abstract MMU Design

The RAM in this design is 16 bit(65536 cell) and is used to store the physical part of the translated addresses. To access the cell containing the physical part, the virtual part must be entered as the ram address.

Listing 3.1: RAM VHDL Code

```

5 entity ram is

6

port (

7

clock : in std_logic;

: in std_logic;

8

we

9

address : in std_logic_vector(15 downto 0);

datain : in std_logic_vector(15 downto 0);

10

11

dataout : out std_logic_vector(15 downto 0)

12

);

13 end entity ram;

14

15 architecture RTL of ram is

16

type ram_type is array (0 to (2**address'length)-1) of

17

std_logic_vector(datain'range);

18

signal ram : ram_type;

signal read_address : std_logic_vector(address'range);

19

20

21 begin

22 RamProc: process(clock) is

23

24

begin

25

if rising_edge(clock) then

if we = '1' then

26

27

ram(to_integer(unsigned(address))) <= datain;</pre>

28

end if;

read_address <= address;</pre>

29

30

end if;

31 end process RamProc;

32

33 dataout <= ram(to_integer(unsigned(read_address)));</pre>

34

35 end architecture RTL;

```

In order to save data at a specified address you have to enable the we signal and then enter the address you want to store and the data for storing.

Figure 3.2: Ram Store Procedure

In order to read from a address you only have to specify the address signal and the dataout signal will become equal to the stored data.

Figure 3.3: Ram Read Procedure

The code for the RAM is written in a versatile way that makes changes easy. For example we can change the width by changing the address length on the line 9.

## 3.2 MMU Top Level

In order to manage the routing and handling of the address a top level is needed. In the top level, user logic must be added to "break" the virt(31 downto 0) signal into two (15 downto 0) signals. The first 16 bits are ported to the phys(15 downto 0) signal, at line 36 and the last 16 bits are ported to the address(15 downto 0) port of the ram component.

Listing 3.2: RAMs Port Map in Top Level

```

29 begin

30 ram1: ram port map (

clock

31

=> clock,

32

we

=> we,

33

address => virt(31 downto 16),

34

datain => datain,

35

dataout => phys(31 downto 16)

36

);

37

phys(15 downto 0) <= virt(15 downto 0);</pre>

38

```

This enables to pair the translated part, sourced from the RAM, with the nontranslated part of the Virtual address.

### 3.3 AXI Interface

In order to include the MMU in a working design we must "encapsulate" is with an AXI4 interface in order to be able to connect it with other IP blocks that implement the same protocol.

The MMU IP will have 2 AXI4 interfaces. One AXI4 Lite Slave port will be utilised as the IPs input from the PS and one AXI4 Lite Master port used from the IP to write on a target(BRAM, DDR e.t.c.)

Figure 3.4: AXI4 Interface Design

#### 3.3.1 Slave AXI Interface

The Slave interface will have 4 Input Registers where input data will be entered. Each register will serve a specific purpose.

| Register | Address    | Use                                  | Size            |

|----------|------------|--------------------------------------|-----------------|

| 0        | 0x43C00000 | Targeted/Translated Address          | 16  bit/32  bit |

| 1        | 0x43C00004 | Write Enable/Association Address     | 1  bit/16  bit  |

| 2        | 0x43C00008 | AXI4 Lite Transaction Initialisation | 1 bit           |

| 3        | 0x43C0000C | Data                                 | 32 bit          |

Table 3.1: MMU Slave Registers

#### $\cdot$ Register 0

This is a 32 bit register that will have dual purpose. In translation mode it will act as the Virtual Address input. In store mode its first 16 bits will be used as the RAM target address.

#### •Register 1

This 32 bit register utilises only 17 bits. Bit 16 is used to control the mode of the MMU. If it is 'true' we are in Store mode. If it is 'false' we are in Translation Mode. The last 16 bits are used only when we are in Store Mode, ie when the 16th bit of Register 1 is '1'. The data that will be stored in the RAM address specified by Register 0, will be input through this Register.

#### •Register 2

Register 2 is a control register that initialises the AXI transaction when enabled. When we enable it (i.e. 0x43C00000 = '1') the MMU writes the data we input on the specified target using the translated address.

#### •Register 3

This is the data input Register. It is a 32 bit Register used as an input for the data we want to store.

Below you can see the port mapping of the MMU module, inside the Slave port and how we assign each Register to the MMUs input.

Listing 3.3: Port Map of MMU in Slave Port

```

mmu_0 : mmu

263

264

port map(

265

virt => slv_reg0,

266

phys => s_out_port0,

267

clock => S_AXI_ACLK,

=> slv_reg1(16),

268

we

269

datain=> slv_reg1(15 downto 0)

270

);

271

s_txn_init <=slv_reg2(0);</pre>

272

273

s_out_port1 <=slv_reg3;</pre>

```

The Slave interface will also have 2 OUT ports(s\_out\_port0 and s\_out\_port1) used for communication between the Slave and Master port, within the IP. These ports will be used to transfer the translated address(line 266) and data(line 273) to the Master port in order for the Master port to perform the AXI write. To initialize the AXI Write on the Master there is a s\_txn\_init out port that is controlled, as marked before, from Register 2(line 272).

### 3.3.2 Master AXI Interface

The master interface will be implemented to enable the IP to complete AXI Writes to other AXI Slave ports in order to store data to specified targets. The address, which at this point is already translated by the MMU in the Slave port, and data are input from the m\_in\_port0 and m\_in\_port1(line 14 and 15) to the Master interface and ported through 2 signals(line 440 and 441) to the M\_AXI\_AWADDR and M\_AXI\_WDATA OUT ports(line 114 and 115).

This essentially tells the Master port where to store the data that it got.

Listing 3.4: Master Port Routing Routine

```

14 m_in_port0 : in std_logic_vector(C_M_AXI_ADDR_WIDTH-1 downto 0);

15 m_in_port1 : in std_logic_vector(C_M_AXI_ADDR_WIDTH-1 downto 0);

.

.

114 M_AXI_AWADDR <= mmu_transfer0;

115 M_AXI_WDATA <= mmu_transfer1;

.

.

440 mmu_transfer0 <= m_in_port0;

441 mmu_transfer1 <= m_in_port1;</pre>

```

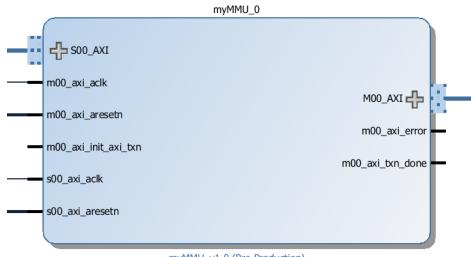

### 3.3.3 Complete IP

After we finish writing and editing the code for the AXI4 Interfaces, with the use of Vivados Create and Package IP tool, we package everything into one IP that can be used in the Block Design environment as a IP Block.

myMMU\_v1.0 (Pre-Production)

Figure 3.5: Packaged MMU IP Block

The tool automatically produces an IP with the appropriate ports that can be later added to a block diagram in Vivados IP Integrator.

The IP, besides the AXI Ports, has various other ports. The most important ports are the Clock ports(axi\_aclk), that provide clock timing to the ports and the reset ports(sxi\_aresetn) that provide reset signaling for the AXI Ports. All the other ports are rendered useless for our purpose.

#### 3.3.4 IP Modes

By completing this IP we get an MMU IP with 2 AXI4 Ports. This MMU has 2 modes. The Translation Mode where it translation of an address will occur, according to the translation table that is configured in the Store mode.

The modes are user swappable and can be controlled through Register 1.

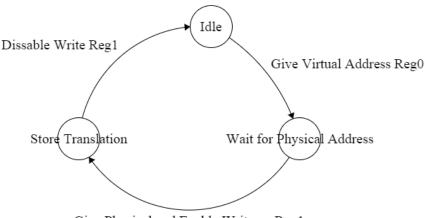

#### Store Mode

Store mode enables us to append a Physical Part to a Virtual Part of an address in order for it to be translated at a later time.

The whole process starts by giving an almost arbitrary 16 bit address, that will serve as the Virtual Part, to Register 0. Then another 16 bit address must be given at Register 1. This will be the 16 bits that the Virtual Address will be translated to. At the same time we have to enable Bit 16 of Register 1 so that the MMU will be put in Store Mode and store the translation in its RAM.

Give Physical and Enable Write on Reg1

Figure 3.6: Store Mode FSM

In the event that we need to perform another Store, Bit 16 of Register 1 must be set to '0' and the process must start from the beginning. If this routine is not followed, overwrite issues may occur.

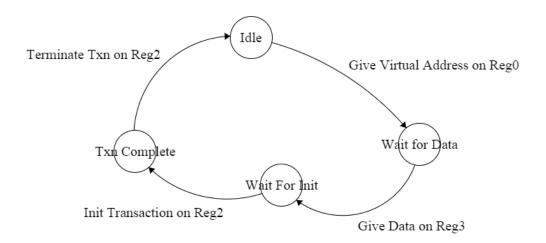

#### Translation Mode

Translation Mode is the "Normal" mode of the MMU in which it accepts a Virtual Address and Data, storing the Data on the Translated Address. It all starts by giving the Virtual Address on Register 0. After that, the Data for storing must be given on Register 3. Then simply enable the AXI Transaction signal on Register 2 and the MMU will translate the address and store the Data on the translated address.

Figure 3.7: Translation Mode FSM

In order to perform another translation, the AXI Transaction signal on Register 2 must be set to "0" again, to avoid overwriting existing data.

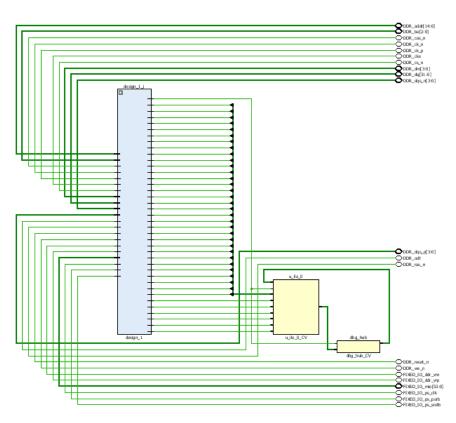

## 3.4 Design

The main focus of the Design is enable us to test multiple scenarios. For example we want to have multiple targets, where we could write, so that we can test the MMUs ability to translate and write on multiple targets as well as in different bases within the same target.

In order to implement the design we use Vivados IP intergrator and we create a new Block Design. Within this Block design we will add our IP Blocks and connect them appropriately

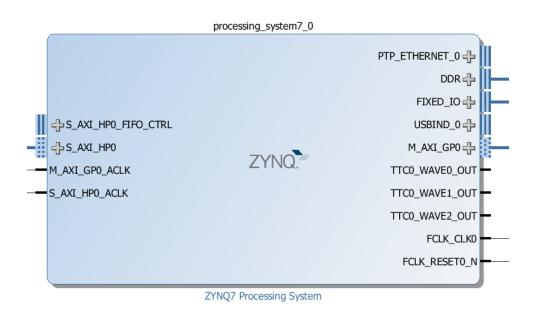

### 3.4.1 PS

The Processing System 7 core is the software interface around the Zynq-7000 platform processing system. The Zynq-7000 family consists of an SoC style integrated PS and a PL unit, providing an extensible and flexible SoC solution on a single die. The Processing System 7 core acts as a logic connection between the PS and the PL while assisting you to integrate customized and embedded IP cores with the processing system using the Vivado  $(\mathbf{\hat{R}})$  IP integrator.

Figure 3.8: Zynq Processing System

The Processing System 7 wrapper instantiates the processing system section of the Zynq®-7000 All Programmable SoC for the programmable logic and external board logic. The wrapper includes unaltered connectivity and, for some signals, some logic functions. For a description of the architecture of the processing system, see the Zynq-7000 All Programmable SoC Technical Reference Manual (UG585)

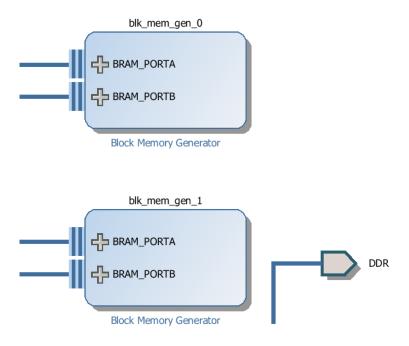

### 3.4.2 Targets

As mentioned before, we need to have multiple targets in order to test various scenarios. For this Design we chose to use 2 Memory Blocks(one 128k and one 8k) and the DDR Memory of the Zedboard.

The Memory Blocks will be Dual Port ones to make us able to access them both from the PS and the MMU.

Figure 3.9: Targets

The MMU IP will access the Block Memory through its AXI4 Master Port. It will also access the DDR but this time through the Zynq PS HP0 AXI4 Port. The Zynq PS will also access the Block Memory through its AXI4 GP0 Port in order to confirm the correct function of the MMU IP.

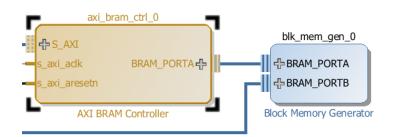

In our design we will use an AXI BRAM Controller to enable us to access the Block Memory through an AXI4 Port. The DDR does not need such a controlled due to the fact that the PS has an integrated DDR Controller

Figure 3.10: AXI BRAM Controller

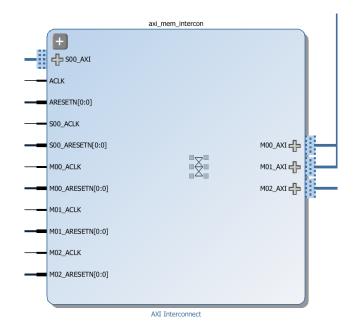

### 3.4.3 AXI Interconnects

The AXI Interconnect core can be added to a Vivado $(\mathbb{R})$  IP integrator block design in the Vivado Design Suite. The Interconnect IP core represents a hierarchical design block that become configured and connected during our system design session.

It allows any mixture of AXI master and slave devices to be connected to it, which can vary from one another in terms of data width, clock domain and AXI subprotocol (AXI4, AXI3, or AXI4 Lite). When the interface characteristics of any connected master or slave device differ from those of the crossbar switch inside the interconnect, the appropriate infrastructure cores are automatically inferred and connected within the interconnect to perform the necessary conversions.

Figure 3.11: Interconnect

In this design we use the AXI Interconnects in order for the MMU and the PS to access all three Targets through one Master port.

### 3.4.4 Complete Design

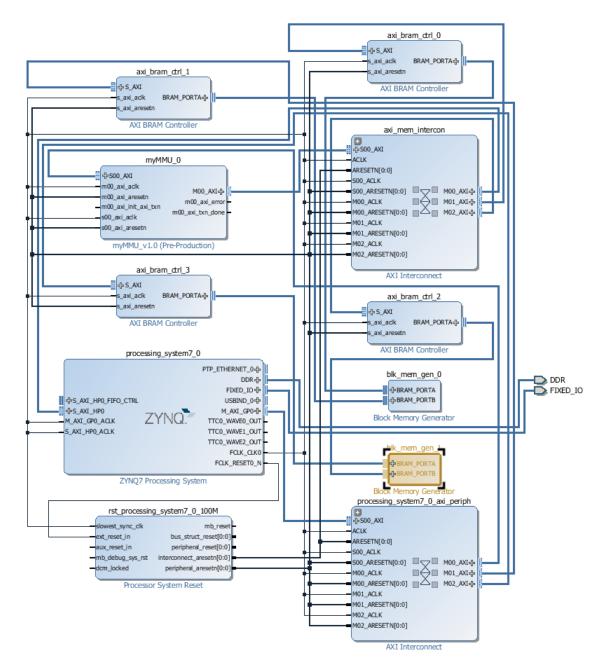

Merging it all together we end up with the following design.

Figure 3.12: Complete Design

Vivado automatically configured the connection with the DDR. After everything is set we let Vivado generate the Bitstream that will later be downloaded on the Zedboard so that we can test the MMU.

## Chapter 4

## Testing

After each stage of implementation, testing is required to ensure the proper function of each component of the IP.

### 4.1 Ram Testing

After we write the HDL code for the RAM we have to ensure that it actually works. The constraints we have is that it needs to be 16 bit wide with 16 bits of data per cell.

#### 4.1.1 TestBench

Listing 4.1: RAM Test Bench

```

44

stimulus: process

45

begin

46

we

<='1';

47

wait for 10 ns;

address <="000000000000000";

48

49

datain <="0000000000000000";</pre>

50

wait for 10 ns;

51

address <="0000000000000001";

52

datain <="0000000000000001";</pre>

53

wait for 10 ns;

address <="11111111111111111";

54

55

datain <="1111111111111111111";</pre>

56

wait for 10 ns;

57

address <="1111111011111110";

datain <="1111111011111110";</pre>

58

59

wait for 10 ns;

60

address <="11111111111111100";

61

datain <="111111111111111100";</pre>

62

wait for 10 ns;

63

--disable writing on ram and read from previously filled cells

64

<='0';

we

```

```

65

wait for 10 ns;

66

address<="0000000000000000";

67

wait for 10 ns;

address<="0000000000000001";

68

69

wait for 10 ns;

70

address<="1111111111111111";

wait for 10 ns;

71

72

address<="11111111111111100";

73

wait for 10 ns;

74

--read from not filled cell for testing

75

address<="1101110111101100";

76

wait for 10 ns;

77

stop_the_clock <= true;</pre>

78

wait;

79

end process;

```

At line 31-35 we declare the component for testing and its port map. At 41-43 we initialise our signals and at 46-62 we fill random cells with random data. The 64th line is used to disable RAM writing and after that we read from the previously written addresses to ensure correct function. At line 75 we read from a non-filled cell for testing reasons.

#### 4.1.2 Results

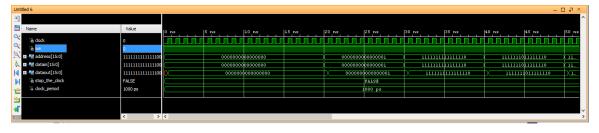

After performing a Behavioural Simulation the waveforms, produced, showed that our writing attempts were successful.

It takes 1 clock cycle to complete one Write on the RAM.

Figure 4.1: RAM Write Simulation

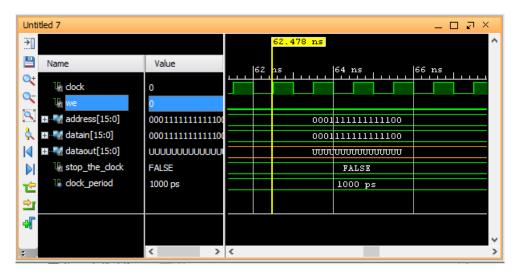

After 60 ns we disable writing and try to read from the cells we previously write on. As the waveforms suggest we have successfully read from the addresses and got valid data back.

Finally we tried to read from a address we did not write on and, as expected, got back invalid data(unsigned).

|                   |               | 60.000 ns |          |          |           |         |                  |       |           |        |           |            |

|-------------------|---------------|-----------|----------|----------|-----------|---------|------------------|-------|-----------|--------|-----------|------------|

| Name              | Value         |           | 65 ns    | 70 ns    | 75 ns     | 80 ns   | 85 ns            | 90 ns | 95 ns     | 100 ns | 105 ns    | 110 ns     |

| 내 dock<br>내 we    | 0<br>0        |           |          |          |           |         |                  |       |           | LUUUU  | nininin   | ייייייי    |

| address[15:0]     | 111111111111  | 11111111  | 1111100  | 00000000 | 00000000  | 0000000 | 00000001         |       | 11111110  |        | 11111100  | 1101110111 |

| 🖬 📲 datain[15:0]  | 1111111111111 |           |          |          |           | 1       | 1111111111111111 | 0     |           |        |           |            |

| 🖬 📲 dataout[15:0] | 111111111111  | 11111111  | 11111100 | 0000000  | 000000000 | 0000000 | 000000001        | Х шшп | 111111110 | Х шиш  | 111111100 | X annanana |

| 1 stop_the_dock   | FALSE         |           |          |          |           |         | FALSE            |       |           |        |           |            |

| 1 dock_period     | 1000 ps       |           |          |          |           |         | 1000 ps          |       |           |        |           |            |

|                   |               |           |          |          |           |         |                  |       |           |        |           |            |

|                   |               |           |          |          |           |         |                  |       |           |        |           |            |

Figure 4.2: RAM Read Simulation

To ensure that we could not write on the ram while the WE signal is enabled, we simulated such situation and as expected we could not write when WE=0.

Figure 4.3: RAM Write Fail

### 4.2 Top Level Testing

After we have successfully tested the RAM module we move on writing a VHDL test bench for the top level of the MMU, which takes care of the bit routing. The objective is to create a module that can accept a 32 bit address and either store and append the first 16 bits with 16 other bits, or translate it based on the stored translation.

#### 4.2.1 TestBench

Our testbench will be very similar with our previous one in terms of testing.

| I | Listing 4 | 1.2: | Top 1 | Level | Simul | lation | $\operatorname{Cod}$ | e |

|---|-----------|------|-------|-------|-------|--------|----------------------|---|

|   |           |      |       |       |       |        |                      |   |

```

37 stimulus: process

38

begin

39

40

-- Put initialisation code here

41

virt

42

datain <="0000000000000000";</pre>

43

<='0';

we

-- Put test bench stimulus code here

44

45

--enable writing on mmu ram and fill some cells with random data

46

<='1';

we

47

wait for 10 ns;

<="00000000000000000000000000000000000";

48

virt

49

datain <="111111111111111111";</pre>

50

wait for 10 ns;

<="00000000000000000000000000000000";

51

virt

52

datain <="111111111111111111";

53

wait for 10 ns;

<="11111111111111100000000000000000";

54

virt

55

datain <="0000000000000001";</pre>

56

wait for 10 ns;

<="11111110111111100000000000000000";

57

virt

58

datain <="000000010000001";</pre>

59

wait for 10 ns;

60

<="11111111111111000000000000000000";

virt

61

datain <="000000000000011";</pre>

62

wait for 10 ns;

63

--disable writing on ram and read from previously filled cells

64

<='0';

we

65

virt <="00011111111111000001111111111100";</pre>

66

wait for 10 ns;

67

68

wait for 10 ns;

69

70

wait for 10 ns;

71

72

wait for 10 ns;

```

```

virt <="111111111111110011111111111111100";</pre>

73

74

wait for 10 ns:

--read from not filled cell for testing

75

virt <="1101110111101100110111011101100";</pre>

76

wait for 10 ns;

77

78

stop_the_clock <= true;</pre>

79

wait;

80

end process;

```

At line 46 "we" is set to '1' so that we can access and write on the RAM. After that we store the virtual part of the address and append it to the physical part. For the virtual part, the first 16 bits of "virt" are used and for the physical part the "datain" is used.

Next we try to translate some addresses by giving a address on "virt". The first 16 bits are the ones that will be translated and the last 16 will remain unchanged, therefore can be random for the purpose of this test.

#### 4.2.2 Results

As we can see from the waveforms our writes were completed successfully.

| Untitled 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         | הם_<br>-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ×        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| <b>→</b> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         | 12.900 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ^        |

| 💾 Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Value                                   | 0 ns   10 ns   20 ns   30 ns   40 ns   50 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60       |

| 🔍 🕌 dock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>n</u> |

| Section 10 we we witt[31:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| Image: Second | 000000000000000000000000000000000000000 | <u>(0000000000000000000000, X000000000, X111111111, X1111110111, X1111111, X1111110111, X111111111, X11111111, X1111111, X1111111, X1111111, X111111, X111111, X11111, X11111, X11111, X1111, X1111, X1111, X1111, X1111, X111, X11, X11</u> | 9        |

| stop_the_dock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | (00000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| Clock_period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1000 ps                                 | 1000 ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |